Programming considerations – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 49

I/O Model Reference

39

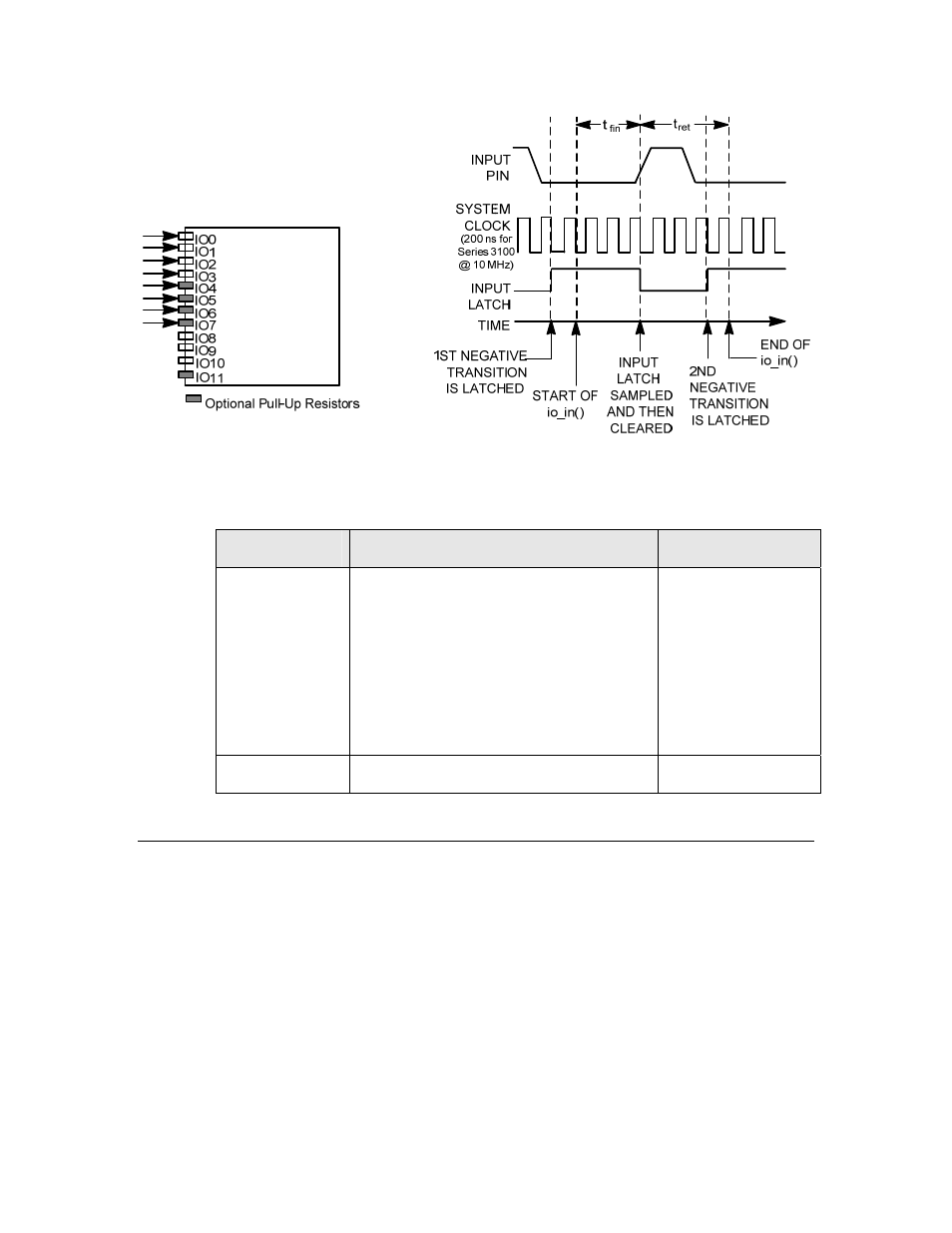

Figure 13. Leveldetect for Series 3100 Devices and Input Timing

Table 15. Leveldetect Input Latency Values for Series 3100 Devices

Symbol

Description

Typical at 10 MHz

t

fin

Function call to sample

IO0

IO1

IO2

IO3

IO4

IO5

IO6

IO7

35 μs

39.4 μs

43.9 μs

48.3 μs

52.7 μs

57.2 μs

61.6 μs

66 μs

t

ret

Return from function

32 μs

Programming Considerations

The state of the input is latched in hardware every 50 ns for a Series 3100 device

with a 40 MHz input clock or every 12.5 ns for a Series 5000 device with an 80

MHz system clock (the interval scales with clock speed), capturing any low level

input. This event is represented by a TRUE (1) value returned from the io_in( )

call, and the value is then cleared to 0 when read. However, as long as the input

pin level stays at logical zero (0), each io_in( ) call returns a 1 value.

The leveldetect input model is useful for capturing events of short duration that

would otherwise be missed by the bit input model. For leveldetect input, the data

type of return_value for io_in( ) is an unsigned short.

For Series 5000 chips, I/O interrupts are also available to implement low-latency

application-specific response to the I/O pins. Because I/O interrupts can be used