Hardware considerations – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 186

176

Timer/Counter Output Models

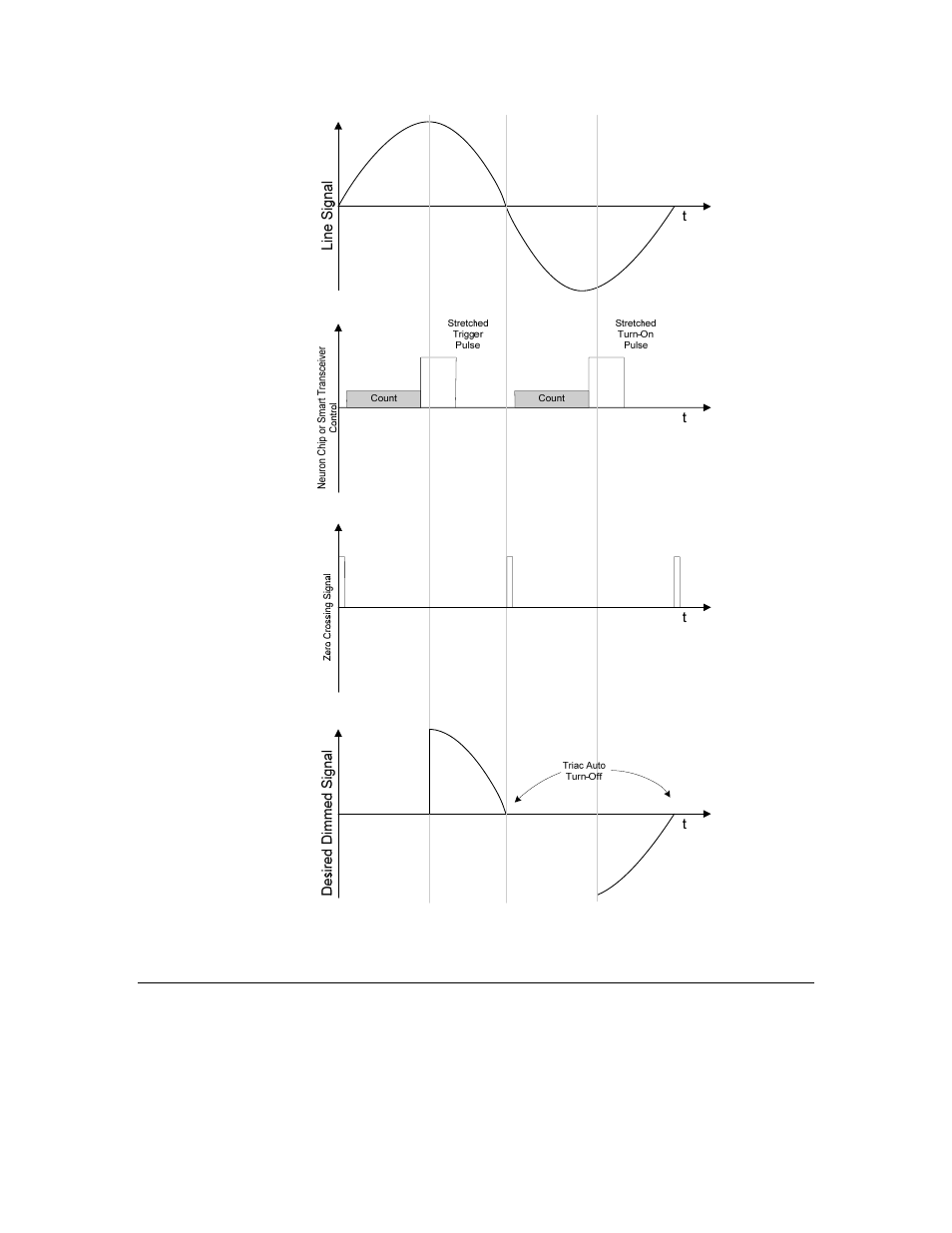

Figure 66. Series 5000 Stretched Triac Output

Hardware Considerations

On a Smart Transceiver, a timer/counter can be configured to control the delay of

an output signal with respect to a synchronization input. This synchronization

can occur on the rising edge, the falling edge, or both the rising and falling edges

of the input signal. For control of AC circuits using a triac device, the sync input

is typically a zero-crossing signal, and the pulse output is the triac trigger signal.