Usage, Example, E clock. table 52 on – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 147

I/O Model Reference

137

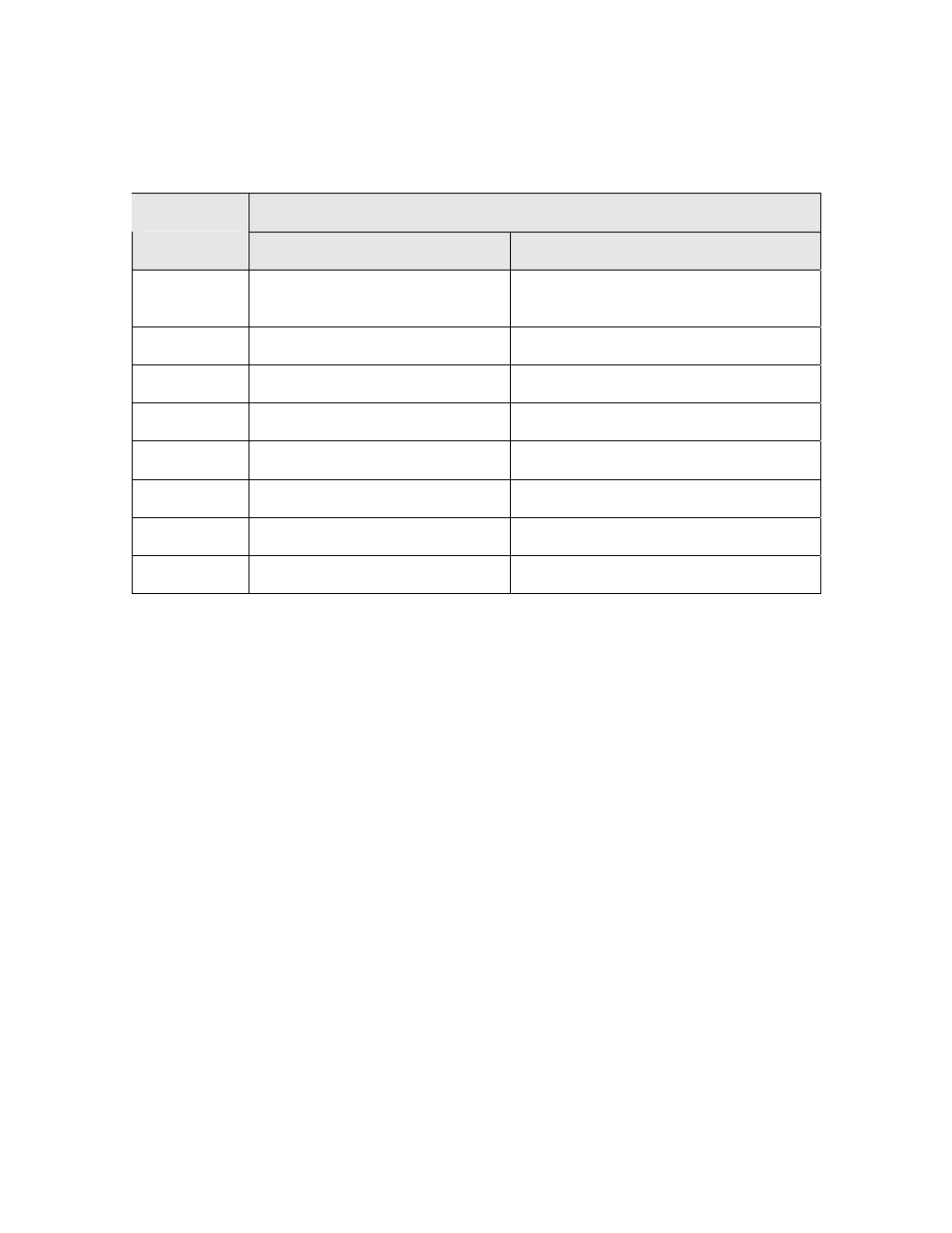

Table 52. Clock Values

Range and Resolution Period

Clock

Series 3100 (10 MHz Clock)

Series 5000 (80 MHz Clock)

0

0 to 13.11 ms in steps of 200 ns

(0-65535)

0 to 1.639 ms in steps of 12.5 ns (0-

65535)

1

0 to 26.21 ms in steps of 400 ns

0 to 3.278 ms in steps of 25 ns

2

0 to 52.42 ms in steps of 800 ns

0 to 6.555 ms in steps of 50 ns

3

0 to 104.86 ms in steps of 1.6 μs

0 to 13.11 ms in steps of 100 ns

4

0 to 209.71 ms in steps of 3.2 μs

0 to 26.21 ms in steps of 200 ns

5

0 to 419.42 ms in steps of 6.4 μs

0 to 52.42 ms in steps of 400 ns

6 (default)

0 to 838.85 ms in steps of 12.8 μs

0 to 104.86 ms in steps of 800 ns

7

0 to 1.677 s in steps of 25.6 μs

0 to 209.71 ms in steps of 1.6 μs

io-object-name

A user-specified name for the I/O object, in the ANSI C format for variable

identifiers.

Usage

unsigned int

bit-count

;

unsigned int

input-buffer

[

buffer-size

];

unsigned long

max-period

,

threshold

;

count

= io_in(

io-object-name

,

input-buffer

,

bit-count

,

max-period

,

threshold

);

Example

This example works with a Series 3100 device and an infrared encoder/decoder

chip that uses the NEC IR protocol. This encoder produces a 9 ms start bit cycle

before the actual data stream. During the start bit cycle, the input signal is

driven low. This start condition is typical of infrared encoders because it allows a

receiver’s or demodulator’s automatic gain control (AGC) circuit time to adjust.

It also gives the Neuron Chip or Smart Transceiver some time to catch this

condition from the scheduler, and enter the io_in( ) function. After the AGC

burst, the protocol includes a 4.5 ms space, which is then followed by 32 bits for

the device address and command.

The NEC protocol uses pulse distance encoding of the bits. Each pulse is a 560 μs

long 38 kHz carrier burst (about 21 cycles). A logical one requires 2.250 ms to

transmit, and a logical zero requires 1.125 ms to transmit. The input clock is 10