Programming considerations, Using the irq signal – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

Page 80

70

Parallel I/O Models

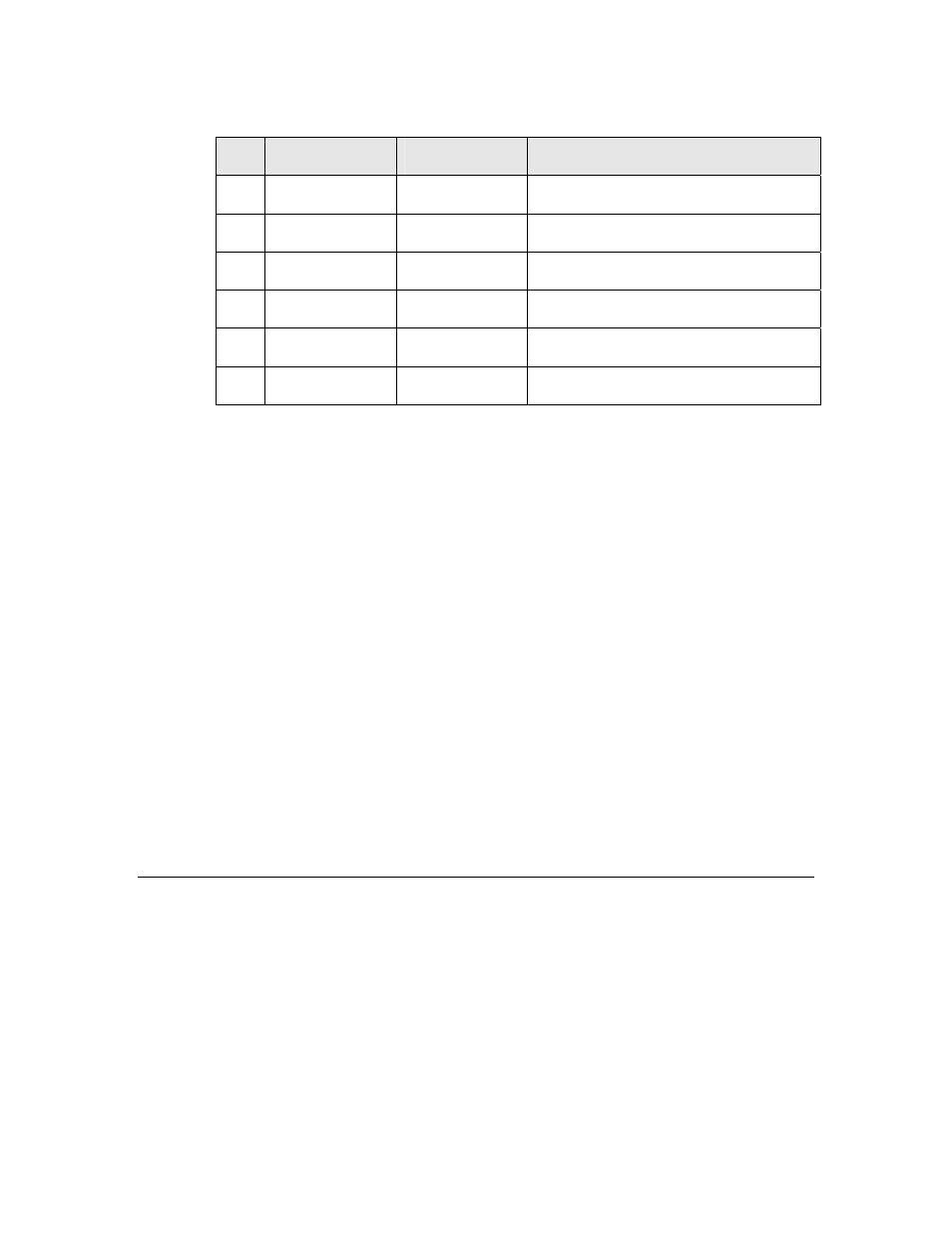

Table 28. Slave Passes Token to Master

Step Master

Slave

Comment

1

(Owns

Token)

2

Write NULL

Slave has no data to send to master

3 Read

NULL

NULL=0x00

4

Write EOM

End of data transfer (EOM=0x00)

5

Process EOM

Exchange token

6 (Owns

Token)

Using the IRQ Signal

A Series 5000 device can use the IRQ pin as an indication that the network is

ready, either for uplink or for downlink. The Neuron C application in the FT

5000 Smart Transceiver or Neuron 5000 Processor would assert the IRQ pin high

to cause an interrupt for the host device.

A downlink ready interrupt would allow the Series 5000 device to inform the host

when it has read the first byte of a transfer. This interrupt would account for the

latency of the parallel interface, that is, between a host write for a downlink

transfer and the Series 5000 device read for the transfer. This latency would be

on the order of 110 microseconds (for a 10 MHz system clock), but it could be

longer if the Series 5000 device is busy processing an incoming network frame.

The host could initiate a downlink transfer by writing only the length byte; it

then could let the interrupt service routine handle the rest of the transfer.

An uplink ready interrupt would provide an indication from the Series 5000

device that uplink traffic needs to be transferred. The IRQ pin would be asserted

only when the Series 5000 device does not own the write token.

The IRQ pin would be deasserted during downlink activity.

Although there are two interrupt cases, there is only a single interrupt request

(IRQ) line. The interrupt type would be determined by the host based on the

state of the Series 5000 device and token ownership.

Programming Considerations

Multiple slave B devices can be connected to a single bus. The difference between

slave A and slave B concerns the use of one of the three control signals (see the

description of the slave, slave_b, and master keywords).

No other I/O objects can be declared on pins IO_0 through IO_10 when the

parallel I/O object is being used.