Clock cycle (user specified) — — — t, Select low to clock transition 4.8 μs — — t, Data out to clock (1st bit of invert mode) 0.5 * t – Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual

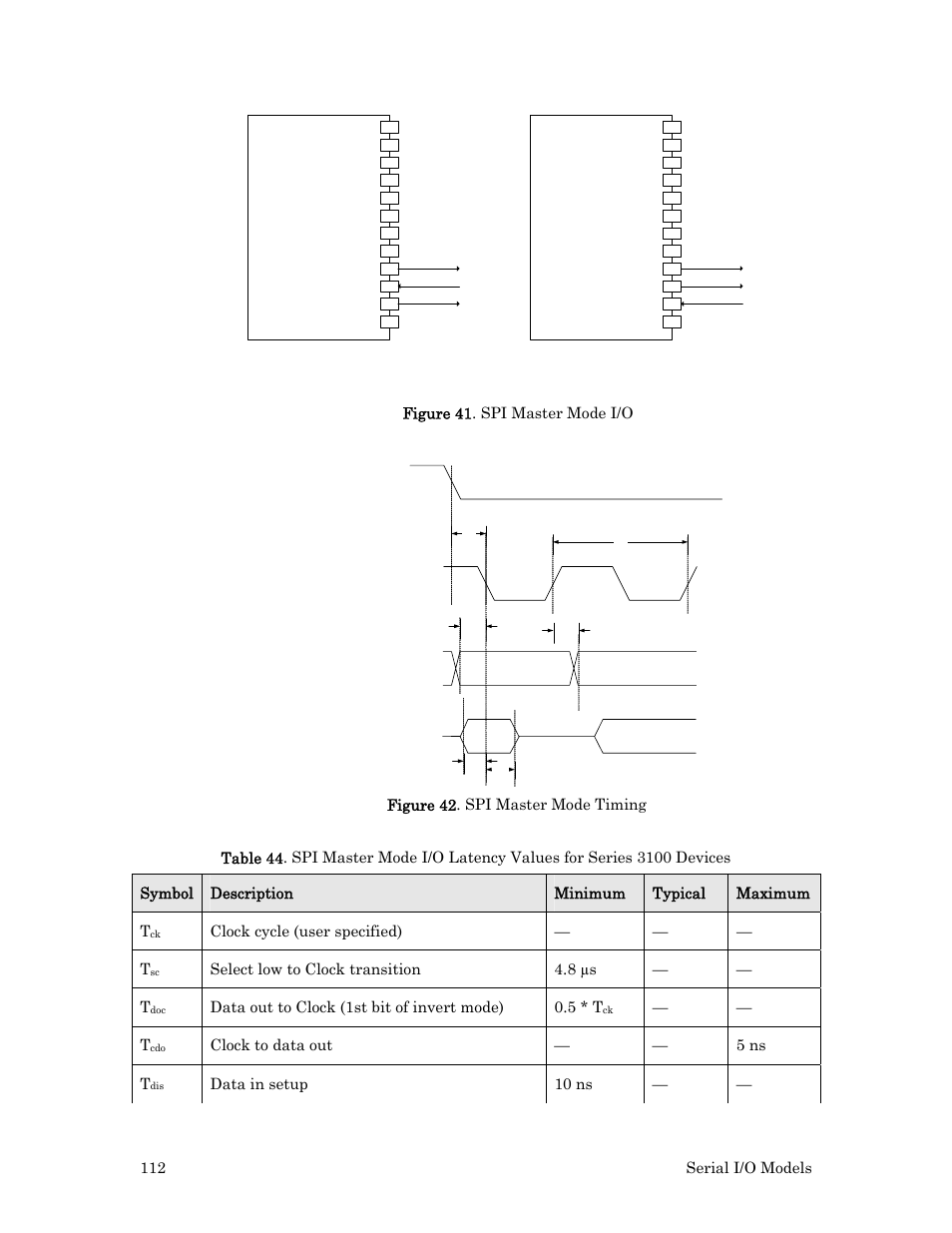

Page 122: Clock to data out — — 5 ns t, Data in setup 10 ns, Spi master, Spi master (neurowire pin mode), Figure 41. spi master mode i/o, Figure 42. spi master mode timing

Clock cycle (user specified) — — — t, Select low to clock transition 4.8 μs — — t, Data out to clock (1st bit of invert mode) 0.5 * t | Clock to data out — — 5 ns t, Data in setup 10 ns, Spi master, Spi master (neurowire pin mode), Figure 41. spi master mode i/o, Figure 42. spi master mode timing | Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual | Page 122 / 209

Clock cycle (user specified) — — — t, Select low to clock transition 4.8 μs — — t, Data out to clock (1st bit of invert mode) 0.5 * t | Clock to data out — — 5 ns t, Data in setup 10 ns, Spi master, Spi master (neurowire pin mode), Figure 41. spi master mode i/o, Figure 42. spi master mode timing | Echelon I/O Model Reference for Smart Transceivers and Neuron Chips User Manual | Page 122 / 209