Ieee 1588v2 feature (dword offset 0xd0 – 0xd6), Ieee 1588v2 feature (dword offset 0xd0 – 0xd6) -16, Ieee 1588v2 feature – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 99: Dword offset 0xd0 – 0xd6)

IEEE 1588v2 Feature (Dword Offset 0xD0 – 0xD6)

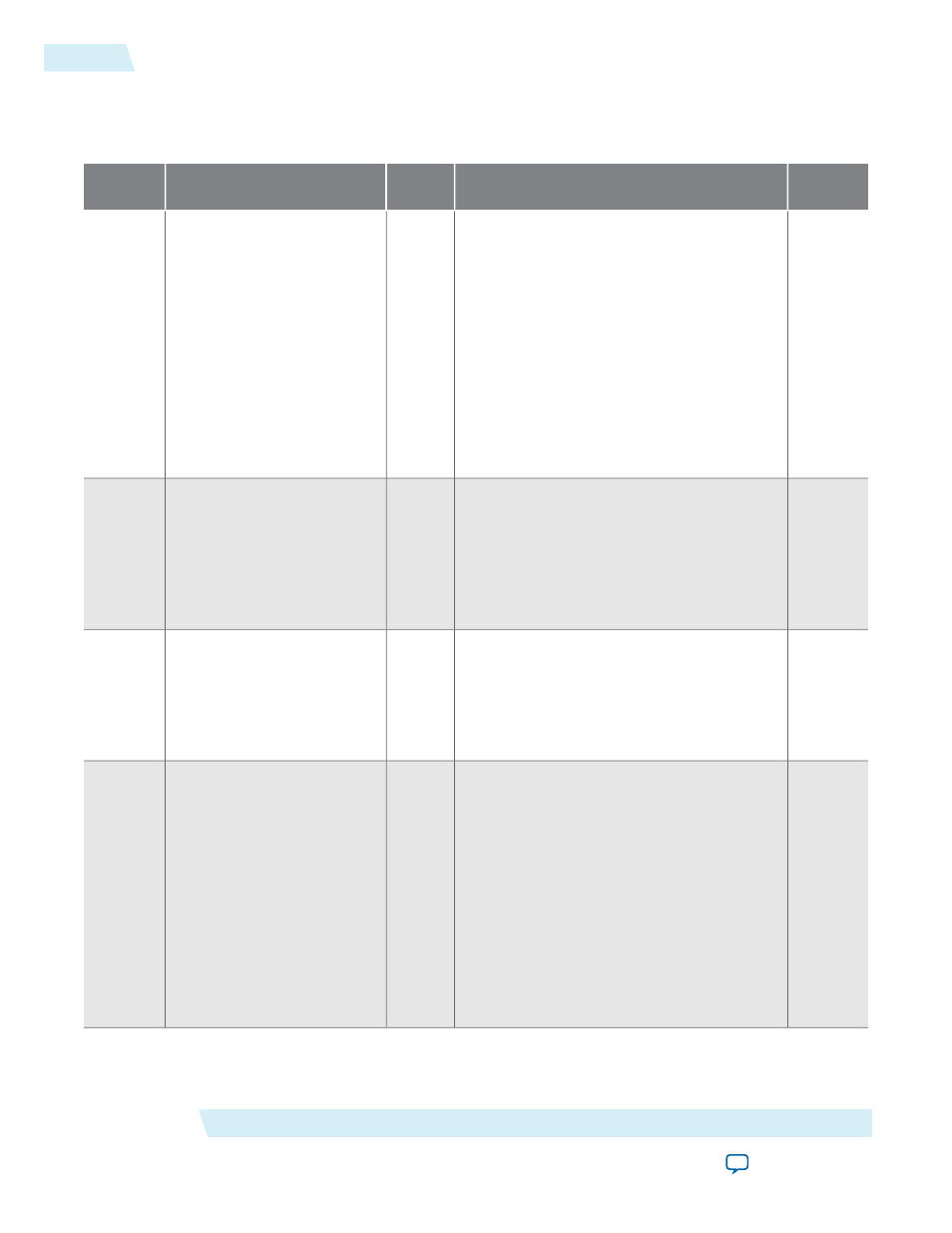

Table 6-7: IEEE 1588v2 MAC Registers

HW Reset

Description

R/W

Name

Dword

Offset

0x0

Clock period for timestamp adjustment on the

transmit datapath. The period register is

multiplied by the number of stages separating

actual timestamp and the GMII bus.

• Bits 0 to 15: Period in fractional nanoseconds

(

TX_PERIOD_FNS

).

• Bits 16 to 24: Period in nanoseconds (

TX_

PERIOD_NS

).

• Bits 25 to 31: Not used.

The default value for the period is 0. For 125-

MHz clock, set this register to 8 ns.

RW

tx_period

0xD0

0x0

Static timing adjustment in fractional

nanoseconds for outbound timestamps on the

transmit datapath.

• Bits 0 to 15: Timing adjustment in fractional

nanoseconds.

• Bits 16 to 31: Not used.

RW

tx_adjust_fns

0xD1

0x0

Static timing adjustment in nanoseconds for

outbound timestamps on the transmit datapath.

• Bits 0 to 15: Timing adjustment in nanosec-

onds.

• Bits 16 to 23: Not used.

RW

tx_adjust_ns

0xD2

0x0

Clock period for timestamp adjustment on the

receive datapath. The period register is

multiplied by the number of stages separating

actual timestamp and the GMII bus.

• Bits 0 to 15: Period in fractional nanoseconds

(

RX_PERIOD_FNS

).

• Bits 16 to 24: Period in nanoseconds (

RX_

PERIOD_NS

).

• Bits 25 to 31: Not used.

The default value for the period is 0. For 125-

MHz clock, set this register to 8 ns.

RW

rx_period

0xD3

Configuration Register Space

Altera Corporation

UG-01008

IEEE 1588v2 Feature (Dword Offset 0xD0 – 0xD6)

6-16

2014.06.30