Altera Triple Speed Ethernet MegaCore Function User Manual

Page 104

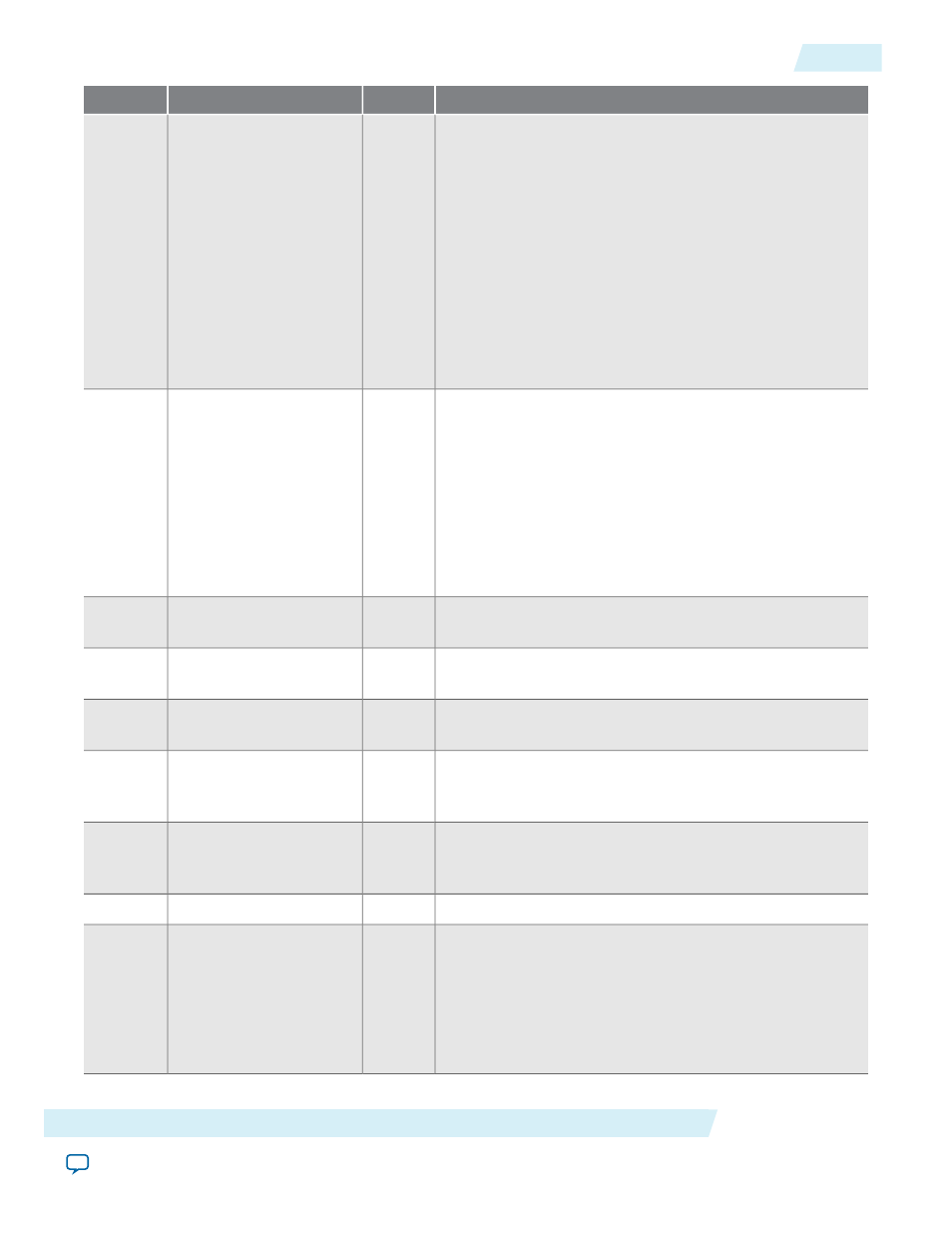

Description

R/W

Name

Bit(s)

Enables the unidirectional function. This bit depends on bit

12. When bit 12 is one, this bit is ignored.

When bit 12 is zero, bit 5 indicates the unidirectional

function:

• A value of 1 enables transmit from media independent

interface regardless of whether the PHY has determined

that a valid link has been established.

• A value of 0 enables transmit from media independent

interface only when the PHY has determined that a valid

link has been established.

The reset value of this bit is zero.

RW

UNIDIRECTIONAL_ENABLE

5

Indicates the operating mode of the PCS function. Bits 6

and 13 are set to 1 and 0 respectively. This combination of

values represent the gigabit mode.

Bit [6, 13]:

• 00: 10 Mbps

• 01: 100 Mbps

• 10: 1 Gigabit

• 11: Reserved

RO

SPEED_SELECTION

6, 13

The PCS function does not support half-duplex mode. This

bit is always set to 0.

RO

COLLISION_TEST

7

The PCS function only supports full-duplex mode. This bit

is always set to 1.

RO

DUPLEX_MODE

8

Set this bit to 1 to restart the auto-negotiation sequence. For

normal operation, set this bit to 0 (reset value).

RW

RESTART_AUTO_

NEGOTIATION

9

Set this bit to 1 to isolate the PCS function from the MAC

layer device. For normal operation, set this bit to 0 (reset

value).

RW

ISOLATE

10

Set this bit to 1 to power down the transceiver quad. The

PCS function then asserts the

powerdown

signal to indicate

the state it is in.

RW

POWERDOWN

11

Set this bit to 1 (reset value) to enable auto-negotiation.

RW

AUTO_NEGOTIATION_ENABLE

12

PHY loopback. Set this bit to 1 to implement loopback in

the GX transceiver. For normal operation, set this bit to 0

(reset value). This bit is ignored if reduced ten-bit interface

(RTBI) is implemented.

This feature is supported in all device families except the

Cyclone IV GX device families.

RW

LOOPBACK

14

Altera Corporation

Configuration Register Space

6-21

Control Register (Word Offset 0x00)

UG-01008

2014.06.30