Altera Triple Speed Ethernet MegaCore Function User Manual

Page 79

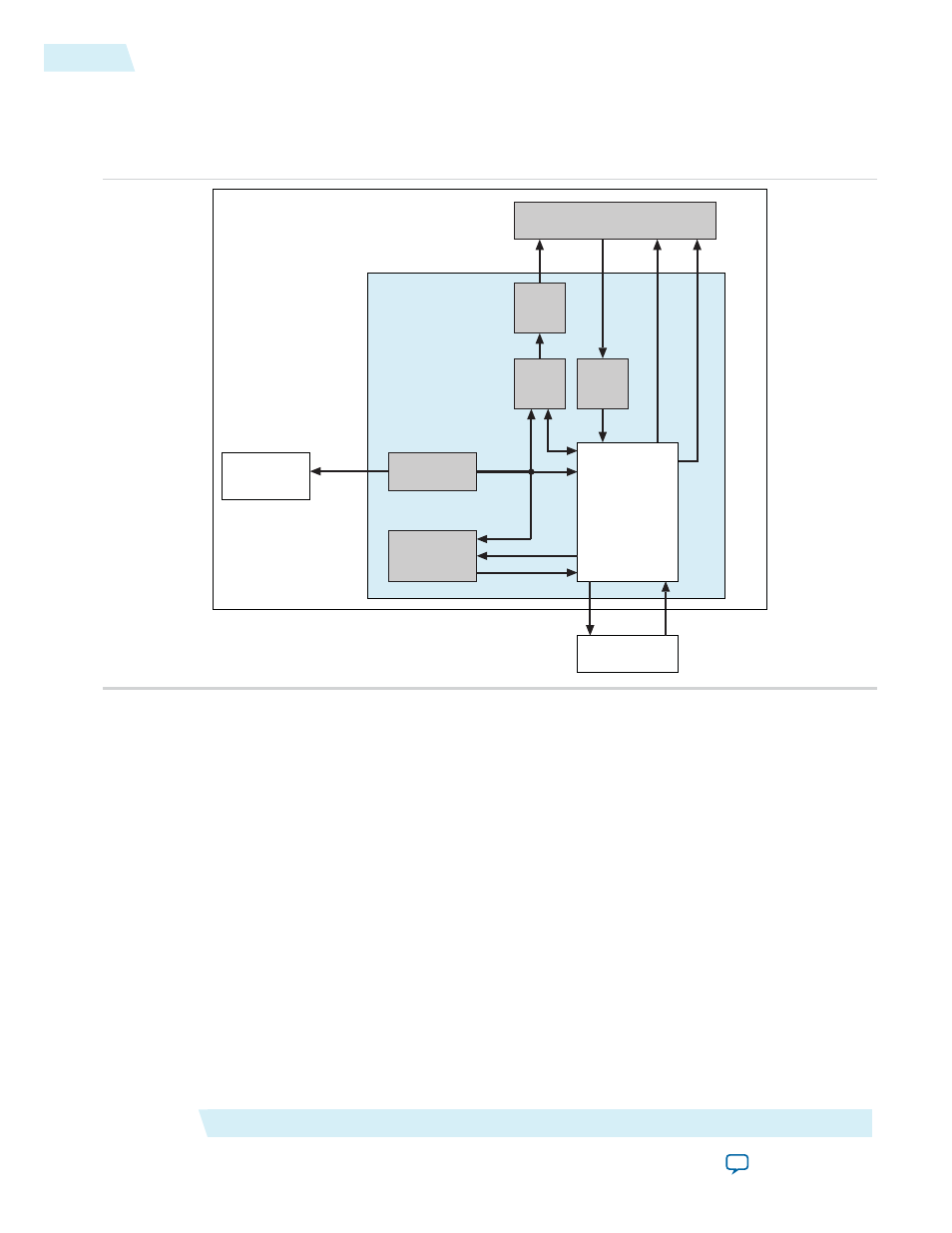

Triple-Speed Ethernet with IEEE 1588v2 Design Example Components

Figure 5-1: Triple-Speed Ethernet MAC with IEEE 1588v2 Design Example Block Diagram

Ethernet

Packet

Classifier

Pulse Per

Second

Module

Time of

Day

Clock

Time of Day

Triple-Speed

Ethernet

Avalon MM Master

Translator

Client Application

(Configuration,

Status & Statistics)

Transceiver

Reconfiguration

Bundle

External PHY

Serial Signal

64-Bit

Avalon ST

Time

of Day

32-Bit

Avalon MM

Reconfiguration

32-Bit

Avalon MM

64-Bit

Avalon ST

Pulse Per

Second

Timestamp &

Fingerprint

Client Application

Altera FPGA

Design Example

The Triple-Speed Ethernet with IEEE 1588v2 design example comprises the following components:

• Triple-Speed Ethernet design that has the following parameter settings:

• 10/100/1000 Mbps Ethernet MAC with 1000BASE-X/SGMII PCS

• SGMII bridge enabled

• Used GXB transceiver block

• Number of port = 1

• Timestamping enabled

• PTP 1-step clock enabled

• Timestamp fingerprint width = 4

• Internal FIFO not used

• Transceiver Reconfiguration Controller—dynamically calibrates and reconfigures the features of the

PHY IP cores.

• Ethernet Packet Classifier—decodes the packet type of incoming PTP packets and returns the decoded

information to the Triple-Speed Ethernet MAC.

• Ethernet ToD Clock—provides 64-bits and/or 96-bits time-of-day to TX and RX of Triple-Speed Ethernet

MAC.

• Pulse Per Second Module—returns pulse per second (pps) to user.

Triple-Speed Ethernet with IEEE 1588v2 Design Example

Altera Corporation

UG-01008

Triple-Speed Ethernet with IEEE 1588v2 Design Example Components

5-2

2014.06.30