Tod clock interface signals, Tod clock avalon-mm control interface signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 203

ToD Clock Interface Signals

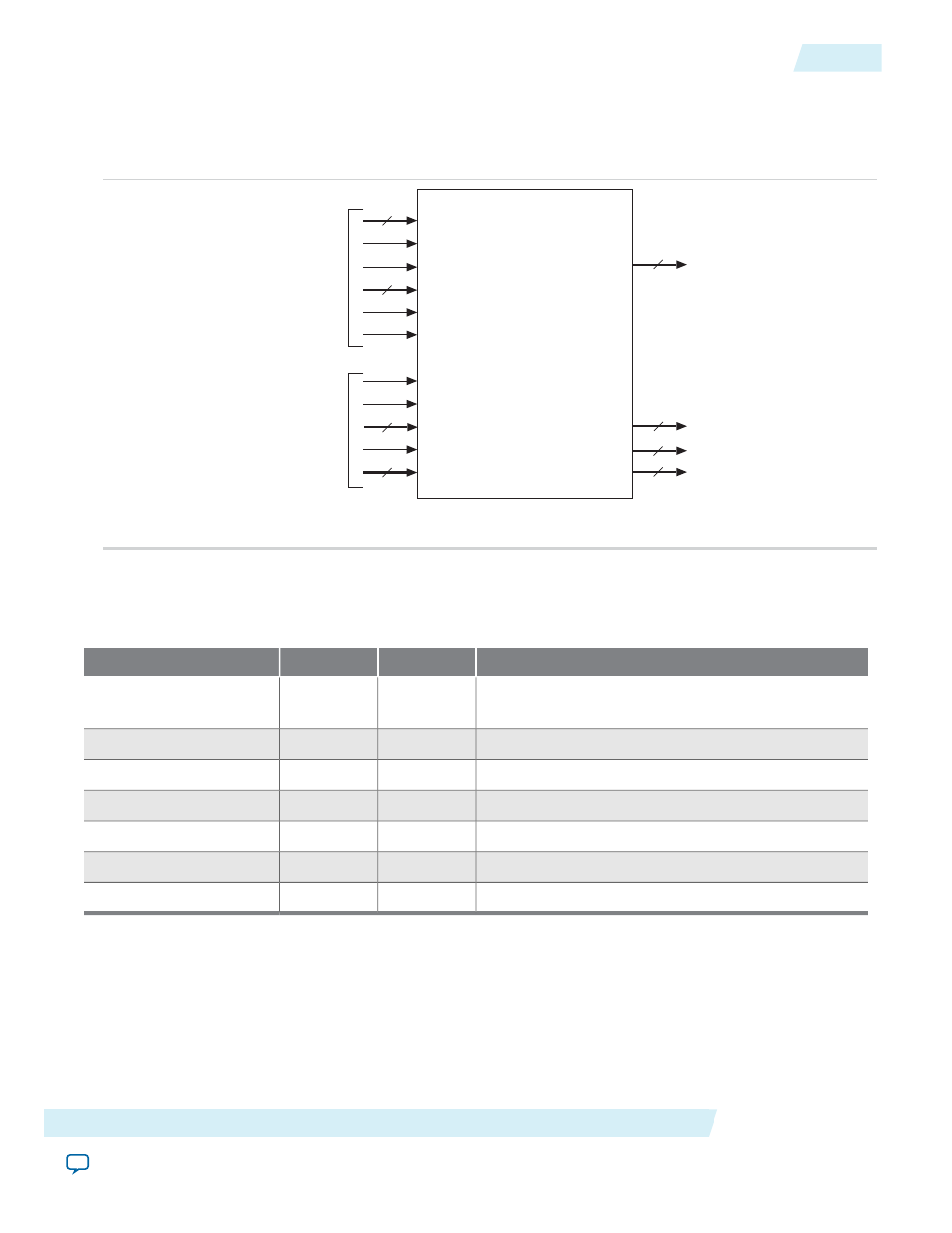

Figure C-1: Time-of-Day Clock Interface Signals

ToD Clock

Avalon-MM

Control

Interface

Signals

csr_readdata[]

32

csr_read

clk

rst_n

csr_write

csr_writedata[]

32

csr_address[]

4

time_of_day_96[]

96

time_of_day_64[]

64

csr_readdata[]

32

time_of_day_96b_load_valid

period_clk

time_of_day_96b_load_data[]

Avalon-ST

Transmit

Interface

Signals

time_of_day_64b_load_valid

time_of_day_64b_load_data[]

64

96

ToD Clock Avalon-MM Control Interface Signals

Table C-4: Avalon-MM Control Interface Signals for ToD Clock

Description

Width

Direction

Signal

Use this bus to specify the register address you want

to read from or write to.

2

Input

csr_address[]

Assert this signal to request a read.

1

Input

csr_read

Carries the data read from the specified register.

32

Output

csr_readdata[]

Assert this signal to request a write.

1

Input

csr_write

Carries the data to be written to the specified register.

32

Input

csr_writedata[]

Register access reference clock.

1

Input

clk

Assert this active low signal to reset the ToD clock.

1

Input

rst_n

Altera Corporation

Time-of-Day (ToD) Clock

C-3

ToD Clock Interface Signals

UG-01008

2014.06.30