Sharing transceiver quads, Exposed ports in the new user interface, Exposed ports in the new user interface -7 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 169

rx_recovclkout

clock must be buffered by two levels of inverter in the top level module so that it can be

fitted to the general I/O pins.

Sharing Transceiver Quads

For designs that contain multiple PMA blocks targeting Altera device families with GX transceivers, you

can combine the transceiver channels in the same quad. To share the same transceiver quad, the transceiver

channels must have the same dynamic reconfiguration setting. In other words, you must turn on dynamic

reconfiguration capabilities in all channels in a quad even though you only intend to use these capabilities

in some of the channels.

The dynamic reconfiguration is always turned on in devices other than Arria GX and Stratix II GX. When

the dynamic reconfiguration is turned on in designs targeting devices other than Stratix V, Altera recommends

that you connect the dynamic reconfiguration signals to the ALTGX_RECONFIG megafunction.

In Stratix V devices, Altera recommends that you connect the dynamic reconfiguration signals to the

Transceiver Reconfiguration Controller megafunction. For transceiver quad sharing between Triple-Speed

Ethernet IP core and other IP cores that target Stratix V devices, reset signal for all the cores must be from

the same source.

Refer to the respective device handbook for more information on dynamic reconfiguration signals in Altera

devices.

Migrating From Old to New User Interface For Existing Designs

In Quartus II software ACDS 13.0 release, the old Triple-Speed Ethernet MegaCore function user interface

is deprecated. Existing Triple-Speed Ethernet designs generated prior to the ACDS 13.0 release can still load

properly in ACDS 13.0. However, starting from ACDS 13.1 release, the old Triple-Speed Ethernet interface

and the design generated using the old interface will not be supported.

You need to manually migrate your design to the new user interface. Reopening and saving the existing

design created with the old user interface will not automatically convert the design to the new user interface.

To migrate your design to the new user interface, launch the Quartus II software ACDS 13.0 or higher, create

a new project, and specify the parameters as described in

on page 2-6.

Exposed Ports in the New User Interface

In the new user interface in Qsys, for a design that has a MAC function, you have to manually connect the

exposed ports or terminate them.

In MAC variation with internal FIFO buffers, the ready latency is two in both standalone and Qsys flow.

The Qsys system inserts a timing adapter to change the ready latency to zero.

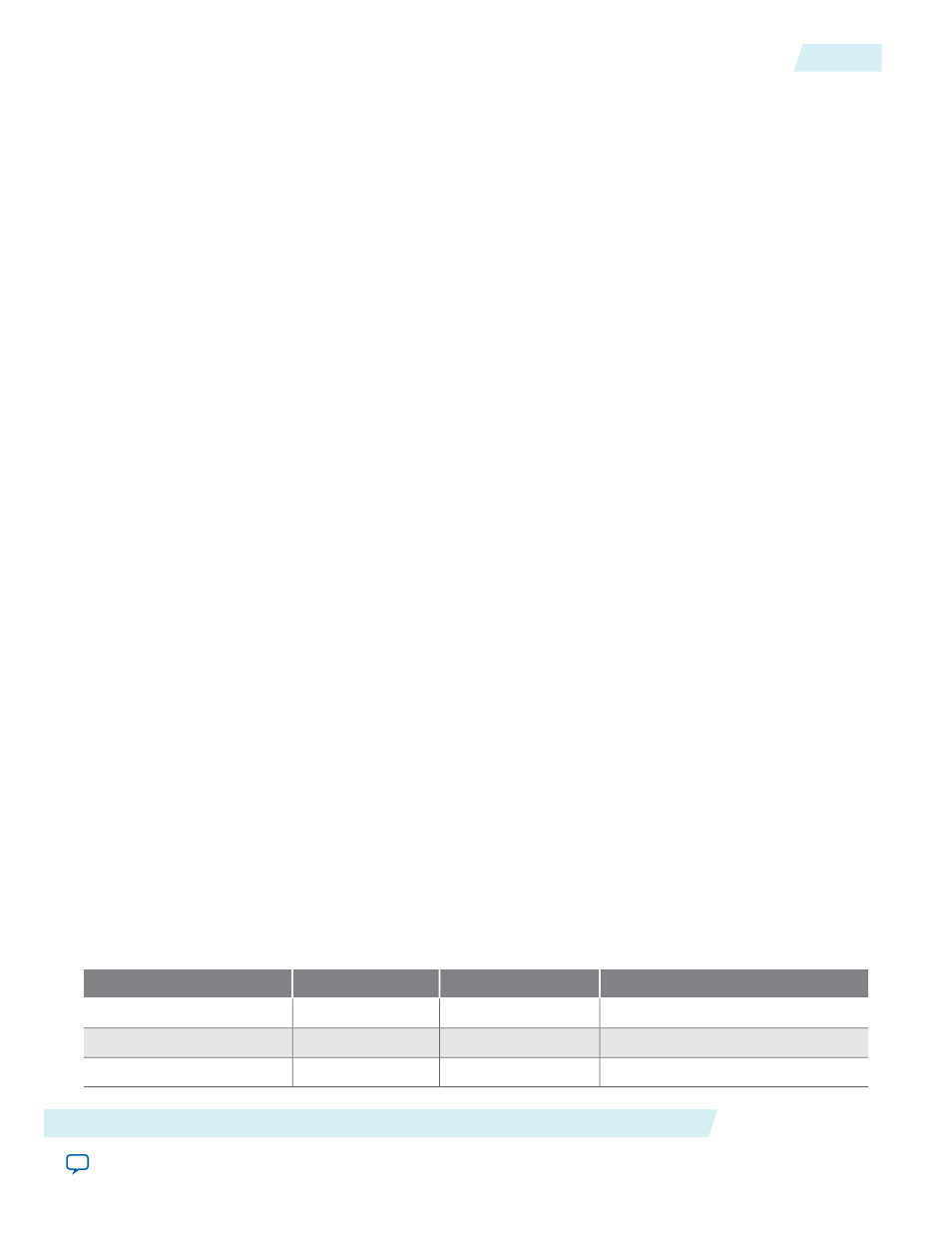

Table 8-2: Exposed Ports and Recommended Termination Value for MAC Variation With Internal FIFO Buffers

Recommended Termination Value

Width

I/O

Port Name

1'b0

1

I

xon_gen

1'b0

1

I

xoff_gen

Left open

1

O

magic_wakeup

Altera Corporation

Design Considerations

8-7

Sharing Transceiver Quads

UG-01008

2014.06.30