An_expansion register (word offset 0x06), If_mode register (word offset 0x14) – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 109

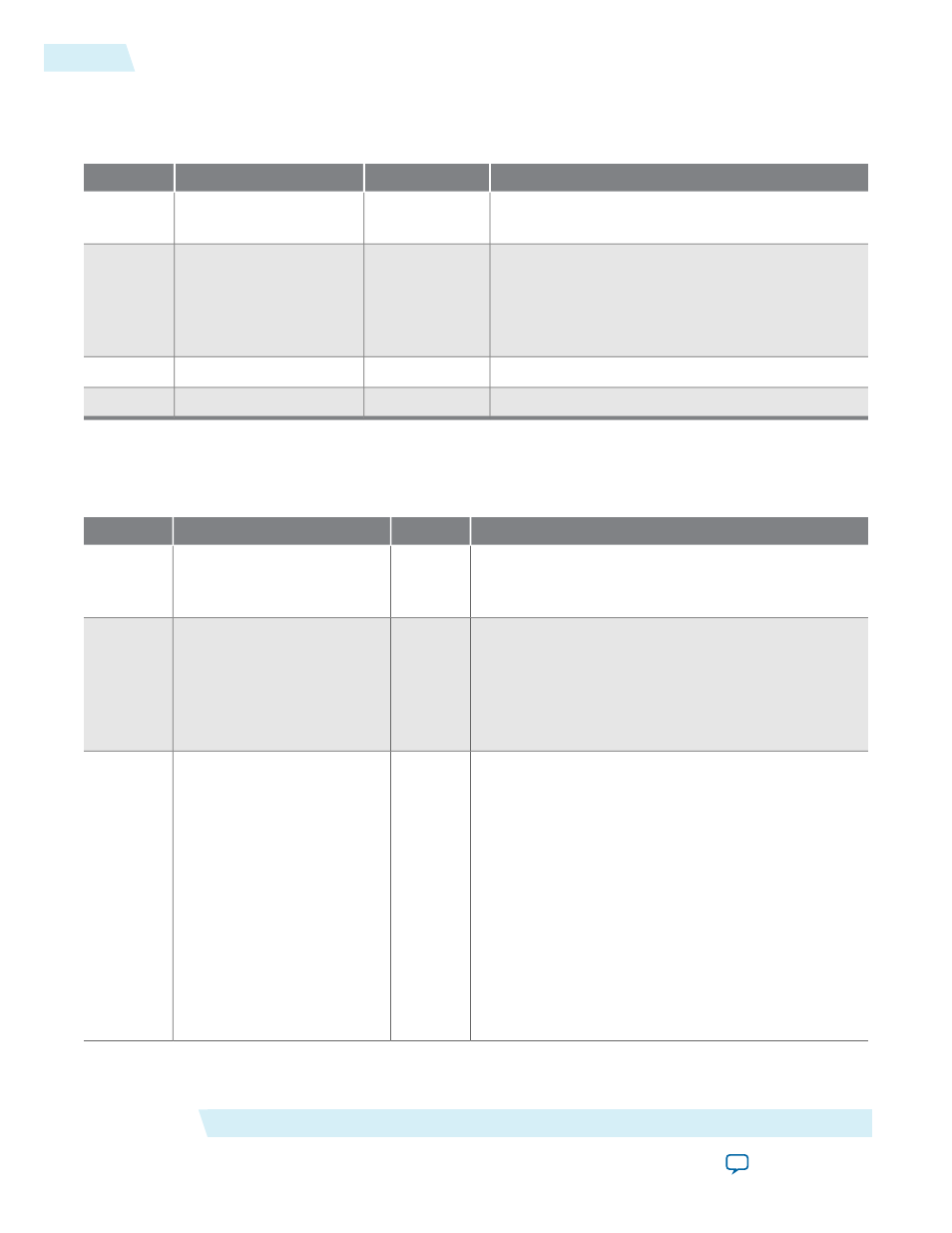

An_Expansion Register (Word Offset 0x06)

Table 6-18: An_Expansion Register Description

Description

R/W

Name

Bit(s)

A value of 1 indicates that the link partner supports

auto-negotiation. The reset value is 0.

RO

LINK_PARTNER_AUTO_

NEGOTIATION_ABLE

0

A value of 1 indicates that a new page is received

with new partner ability available in the register

partner_ability

. The bit is set to 0 (reset value)

when the system management agent performs a

read access.

RO

PAGE_RECEIVE

1

Unused. Always set to 0.

—

NEXT_PAGE_ABLE

2

—

—

Reserved

15:3

If_Mode Register (Word Offset 0x14)

Table 6-19: IF_Mode Register Description

Description

R/W

Name

Bit(s)

Determines the PCS function operating mode. Setting

this bit to 1 enables SGMII mode. Setting this bit to 0

enables 1000BASE-X gigabit mode.

RW

SGMII_ENA

0

This bit applies only to SGMII mode. Setting this bit

to 1 causes the PCS function to be configured with the

link partner abilities advertised during auto-negotia-

tion. If this bit is set to 0, it is recommended for the

PCS function to be configured with the

SGMII_SPEED

and

SGMII_DUPLEX

bits.

RW

USE_SGMII_AN

1

SGMII speed. When the PCS function operates in

SGMII mode (

SGMII_ENA

= 1) and programed not to

be automatically configured (

USE_SGMII_AN

= 0), set

the speed as follows:

• 00: 10 Mbps

• 01: 100 Mbps

• 10: 1 Gigabit

• 11: Reserved

These bits are ignored when

SGMII_ENA

is 0 or

USE_

SGMII_AN

is 1. These bits are only valid if you only

enable the SGMII mode and not the auto-negotiation

mode.

RW

SGMII_SPEED[1:0]

3:2

Configuration Register Space

Altera Corporation

UG-01008

An_Expansion Register (Word Offset 0x06)

6-26

2014.06.30