Ieee 1588v2 tx timestamp request signals, Ieee 1588v2 tx insert control timestamp signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 144

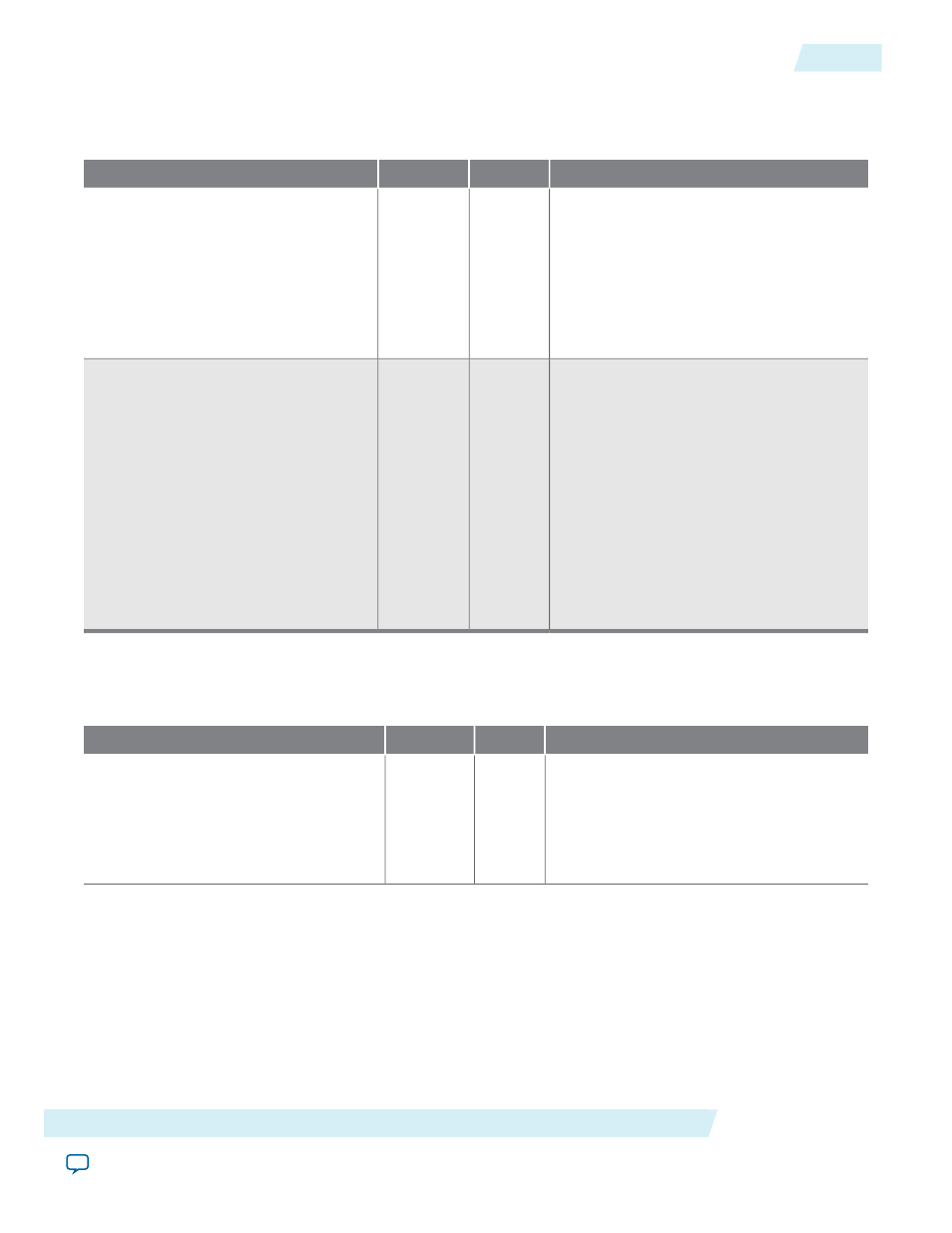

IEEE 1588v2 TX Timestamp Request Signals

Table 7-31: IEEE 1588v2 TX Timestamp Request Signals

Description

Width

I/O

Signal

Assert this signal when a user-defined

tx_

egress_timestamp

is required for a

transmit frame.

Assert this signal in the same clock cycle

as the start of packet (

avalon_st_tx_

startofpacket

or

avalon_st_tx_

startofpacket_n

is asserted).

1

I

tx_egress_timestamp_request_

valid_n

Use this bus to specify fingerprint for the

user-defined

tx_egress_timestamp

. The

fingerprint is used to identify the user-

defined timestamp.

The signal width is determined by the

TSTAMP_FP_WIDTH parameter (default

parameter value is 4).

The value of this signal is mapped to

user_

fingerprint

.

This signal is only valid when you assert

tx_egress_timestamp_request_valid

.

n

I

tx_egress_timestamp_request_

fingerprint

IEEE 1588v2 TX Insert Control Timestamp Signals

Table 7-32: IEEE 1588v2 TX Insert Control Timestamp Interface Signals

Description

Width

I/O

Signal

Assert this signal to insert egress timestamp

into the associated frame.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

1

I

tx_etstamp_ins_ctrl_timestamp_

insert_n

Altera Corporation

Interface Signals

7-29

IEEE 1588v2 TX Timestamp Request Signals

UG-01008

2014.06.30