Altera ieee 1588v2 feature, Ieee 1588v2 supported configurations, Altera ieee 1588v2 feature -35 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 71: Ieee 1588v2 supported configurations -35

Figure 4-24: Reset Distribution in PCS with Embedded PMA

PMA

Reset

Sequencer

Reset

Synchronizer

Reset

Synchronizer

PCS

reset

reset_tx_clk

reset_rx_clk

gbx_pwrdn_in

rx_freqlocked

For more information about the

rx_freqlocked

signal and transceiver reset, refer to the transceiver handbook

of the respective device family.

Assert the

reset

or

gxb_pwrdn_in

signals to perform a hardware reset on MAC with PCS and embedded

PMA variation.

You must assert the

reset

signal for at least three clock cycles.

Note:

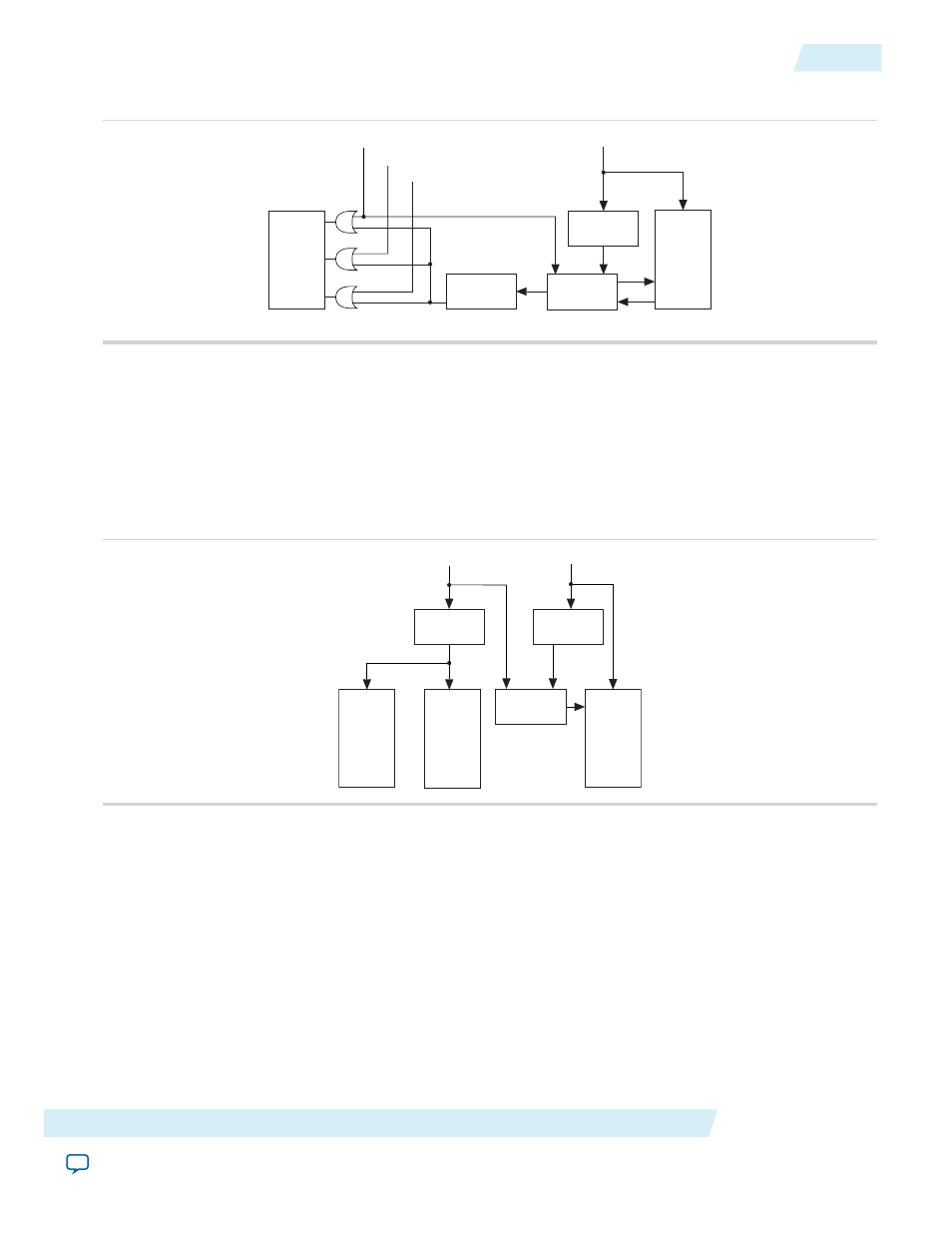

Figure 4-25: Reset Distribution in MAC with PCS and Embedded PMA

PMA

Reset

Sequencer

Reset

Synchronizer

Reset

Synchronizer

MAC

reset

gbx_pwrdwn

PCS

Altera IEEE 1588v2 Feature

The Altera IEEE 1588v2 feature provides timestamp for receive and transmit frames in the Triple-Speed

Ethernet MegaCore function designs. The feature consists of Precision Time Protocol (PTP). PTP is a layer-3

protocol that accurately synchronizes all real time-of-day clocks in a network to a master clock.

This feature is supported in Arria V, Arria 10, Cyclone V, MAX10, and Stratix V device families.

IEEE 1588v2 Supported Configurations

The Triple-Speed Ethernet MegaCore functions support the IEEE 1588v2 feature only in the following

configurations:

Altera Corporation

Functional Description

4-35

Altera IEEE 1588v2 Feature

UG-01008

2014.06.30