Mac receive interface signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 119

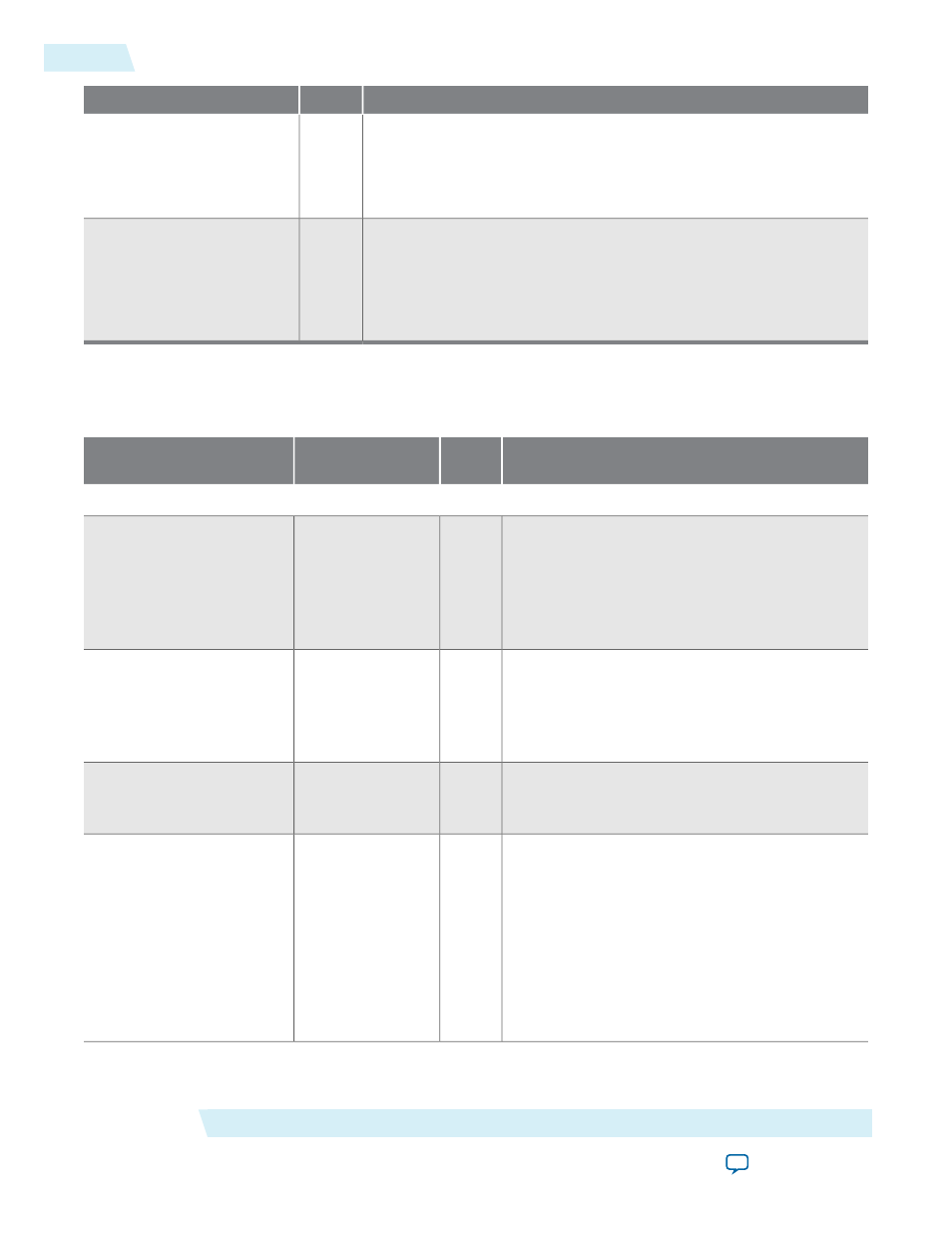

Description

I/O

Name

Gigabit mode selection. Can be driven to 1 by an external device, for

example a PHY device, to set the MAC function to operate in gigabit.

When set to 0, the MAC is set to operate in 10/100 Mbps. This signal

is ignored when the

ETH_SPEED

bit in the

command_config

register is

set to 1.

I

set_1000

10 Mbps selection. Can be driven to 1 by an external device, for example

a PHY device, to indicate that the MAC function is connected to a 10-

Mbps PHY device. When set to 0, the MAC function is set to operate

in 100-Mbps or gigabit mode. This signal is ignored when the

ETH_

SPEED

or

ENA_10

bit in the

command_config

register is set to 1. The

ENA_10

bit has a higher priority than this signal.

I

set_10

MAC Receive Interface Signals

Table 7-5: MAC Receive Interface Signals

Description

I/O

Avalon-ST Signal

Type

Name

Avalon-ST Signals

Receive clock. All signals on the Avalon-ST receive

interface are synchronized on the rising edge of

this clock. Set this clock to the frequency required

to get the desired bandwidth on this interface.

This clock can be completely independent from

rx_clk

.

I

clk

ff_rx_clk

Receive data valid. When asserted, this signal

indicates that the data on the following signals are

valid:

ff_rx_data[(DATAWIDTH -1):0]

,

ff_rx_

sop

,

ff_rx_eop

,

rx_err[5:0]

,

rx_frm_

type[3:0]

, and

rx_err_stat[17:0]

.

O

valid

ff_rx_dval

Receive data. When

DATAWIDTH

is 32, the first byte

received is

ff_rx_data[31:24]

followed by

ff_

rx_data[23:16]

and so forth.

O

data

ff_rx_data

[(DATAWIDTH-1):0]

Receive data modulo. Indicates invalid bytes in

the final frame word:

• 11:

ff_rx_data[23:0]

is not valid

• 10:

ff_rx_data[15:0]

is not valid

• 01:

ff_rx_data[7:0]

is not valid

• 00:

ff_rx_data[31:0]

is valid

This signal applies only when

DATAWIDTH

is set to

32.

O

empty

ff_rx_mod[1:0]

Interface Signals

Altera Corporation

UG-01008

MAC Receive Interface Signals

7-4

2014.06.30