Multiport mac fifo status signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 130

Description

I/O

Avalon-ST Signal

Type

Name

Classification presented at the beginning of each

packet:

Bit 4—Set to 1 for unicast frames.

Bit 3—Set to 1 for broadcast frames.

Bit 2—Set to 1 for multicast frames.

Bit 1—Set to 1 for VLAN frames.

Bit 0—Set to 1 for stacked VLAN frames.

O

data

pkt_class_data

_n[4:0]

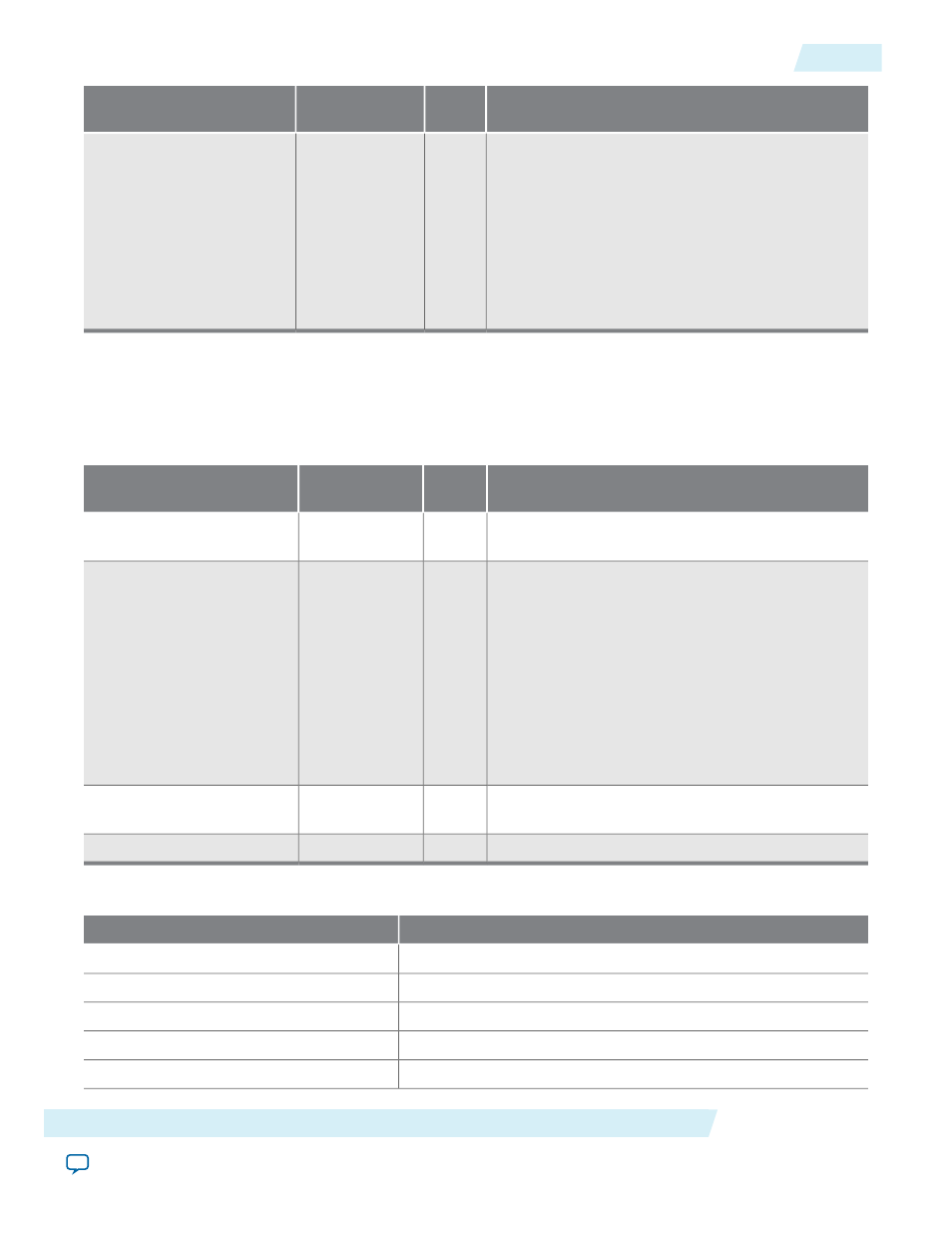

Multiport MAC FIFO Status Signals

The MAC FIFO status interface is an Avalon-ST sink port which streams in information on the fill level of

the external FIFO buffer to the MAC function.

Table 7-17: MAC FIFO Status Signals

Description

I/O

Avalon-ST Signal

Type

Signal Name

Assert this signal to indicate that the fill level of the

external FIFO buffer,

rx_afull_data

_n[1:0],is valid.

I

valid

rx_afull_valid_

n

Carries the fill level of the external FIFO buffer:

rx_afull_data

_n[1]—Set to 1 if the external receive

FIFO buffer reaches the initial warning level

indicating that it is almost full. Upon detecting this,

the MAC function generates pause frames.

rx_afull_data

_n[0]—Set to 1 if the external receive

FIFO buffer reaches the critical level before it

overflows. The FIFO buffer can be considered

overflow if this bit is set to 1 in the middle of a

packet transfer.

I

data

rx_afull_data

_n[1:0]

The port number the status applies to.

I

channel

rx_afull_channel

[(CHANNEL_WIDTH-1):0]

The clock that drives the MAC FIFO status interface.

I

clk

rx_afull_clk

Table 7-18: References

Section

Interface Signal

on page 7-2

Clock and reset signals

on page 7-3

MAC control interface

MAC Transmit Interface Signals

on page 7-6

MAC transmit interface

on page 7-4

MAC receive interface

on page 7-3

Status signals

Altera Corporation

Interface Signals

7-15

Multiport MAC FIFO Status Signals

UG-01008

2014.06.30