Altera Triple Speed Ethernet MegaCore Function User Manual

Page 147

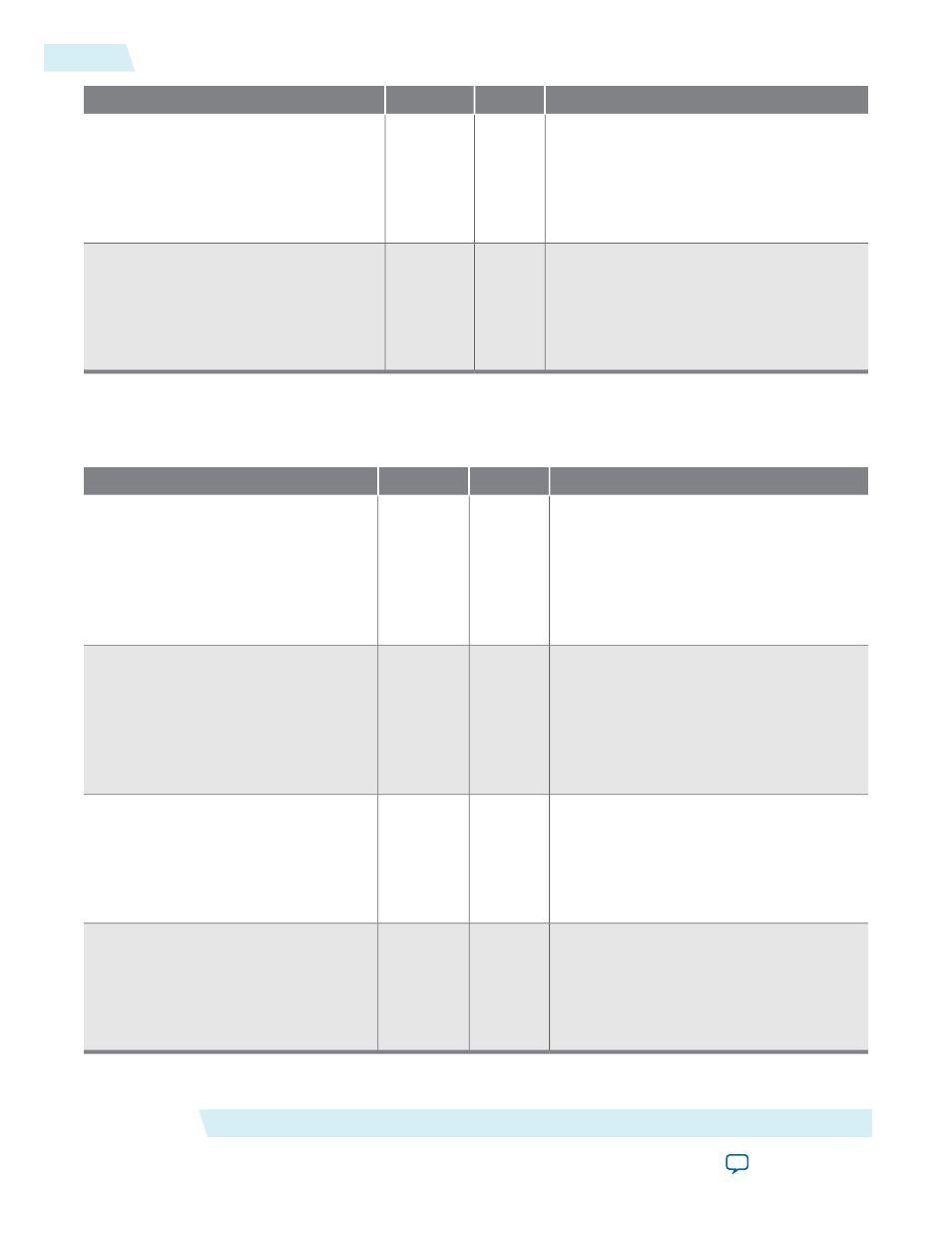

Description

Width

I/O

Signal

The location of the checksum field, relative

to the first byte of the packet.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

16

I

tx_etstamp_ins_ctrl_offset_

checksum_field[]

The location of the checksum correction

field, relative to the first byte of the packet.

Assert this signal in the same clock cycle as

the start of packet (

avalon_st_tx_

startofpacket

is asserted).

16

I

tx_etstamp_ins_ctrl_offset_

checksum_correction[]

IEEE 1588v2 Time-of-Day (ToD) Clock Interface Signals

Table 7-33: IEEE 1588v2 ToD Clock Interface Signals

Description

Width

I/O

Signal

Use this bus to carry the time-of-day from

external ToD module to 96-bit MAC TX

clock.

Consists of 48 bits seconds field, 32 bits

nanoseconds field, and 16 bits fractional

nanoseconds field

96

I

tx_time_of_day_96b_data_n

Use this bus to carry the time-of-day from

external ToD module to 96-bit MAC RX

clock.

Consists of 48 bits seconds field, 32 bits

nanoseconds field, and 16 bits fractional

nanoseconds field

96

I

rx_time_of_day_96b_data

Use this bus to carry the time-of-day from

external ToD module to 64-bit MAC TX

clock.

Consists of 48-bit nanoseconds field and

16-bit fractional nanoseconds field

64

I

tx_time_of_day_64b_data

Use this bus to carry the time-of-day from

external ToD module to 64-bit MAC RX

clock.

Consists of 48-bit nanoseconds field and

16-bit fractional nanoseconds field

64

I

rx_time_of_day_64b_data

Interface Signals

Altera Corporation

UG-01008

IEEE 1588v2 Time-of-Day (ToD) Clock Interface Signals

7-32

2014.06.30