Timing, Avalon-st receive interface, Timing -39 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 154: Avalon-st receive interface -39, Table 7-43: references

Table 7-43: References

Section

Interface Signal

on page 7-35

Reset signals

MII/GMII Clocks and Clock Enablers

on page 7-35

MII/GMII clocks and clock enablers

on page 7-35

PCS control interface

on page 7-36

GMII signals

on page 7-36

MII signals

on page 7-37

SGMII status signals

on page 7-23

1.25 Gbps Serial Signals

on page 7-17

Status LED signals

on page 7-17

SERDES control signals

on page 7-23

Transceiver Native PHY signal

Timing

This section shows the timing on the Triple-Speed Ethernet transmit and receive interfaces as well as the

timestamp signals for the IEEE 1588v2 feature.

Related Information

More information on Avalon-MM control interface timing

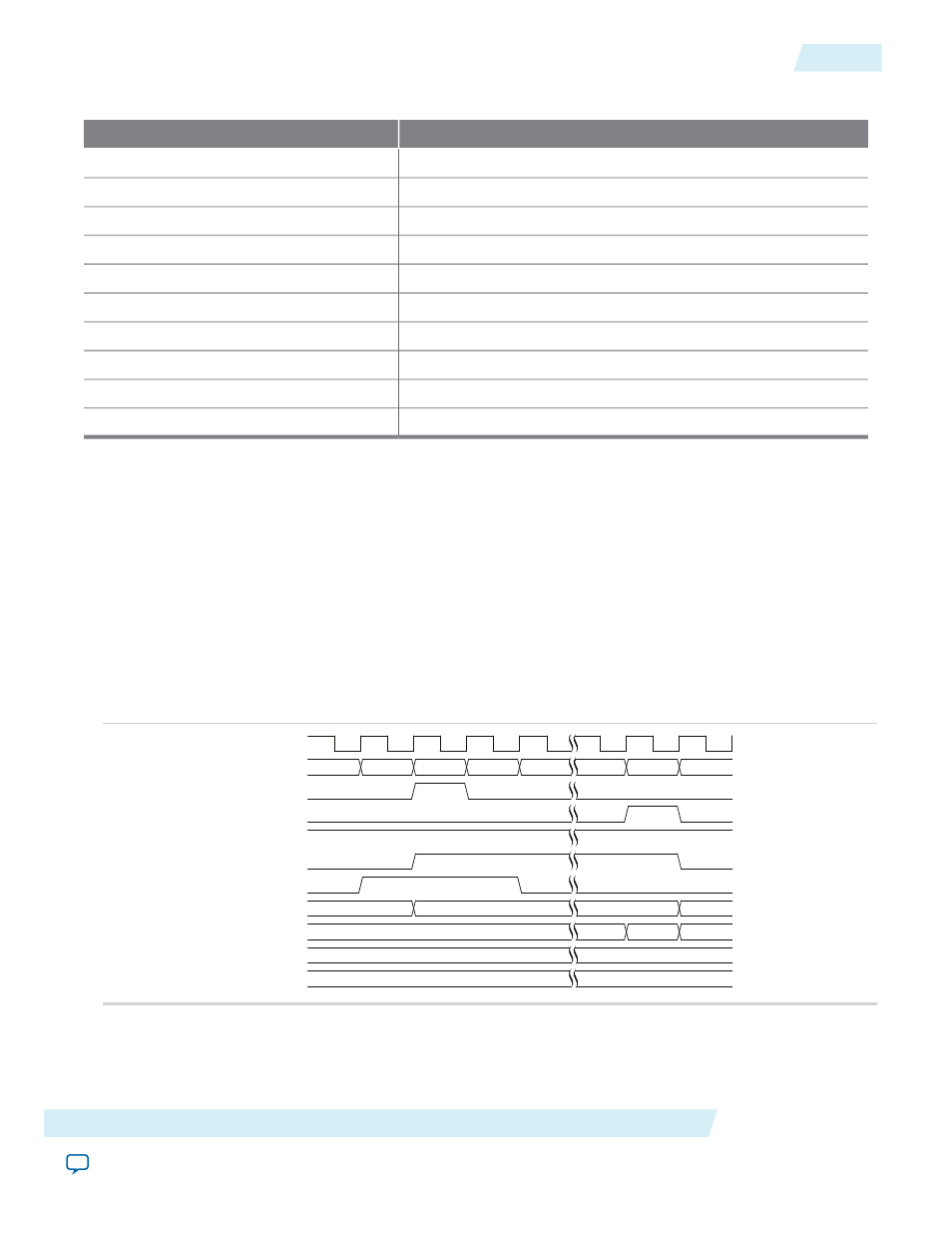

Avalon-ST Receive Interface

Figure 7-10: Receive Operation—MAC With Internal FIFO Buffers

ff_rx_clk

ff_rx_data[31:0]

ff_rx_sop

ff_rx_eop

ff_rx_rdy

ff_rx_dval

ff_rx_dsav

rx_frm_type[3:0]

rx_err_stat[17:0]

rx_err[5:0]

ff_rx_mod[1:0]

00000000

00000000

00000000

00000001

00000002

00000003

00000004

00000005

00000000

00

1

0

00000

00000

00064

00000

00

0

Altera Corporation

Interface Signals

7-39

Timing

UG-01008

2014.06.30