Altera Triple Speed Ethernet MegaCore Function User Manual

Page 17

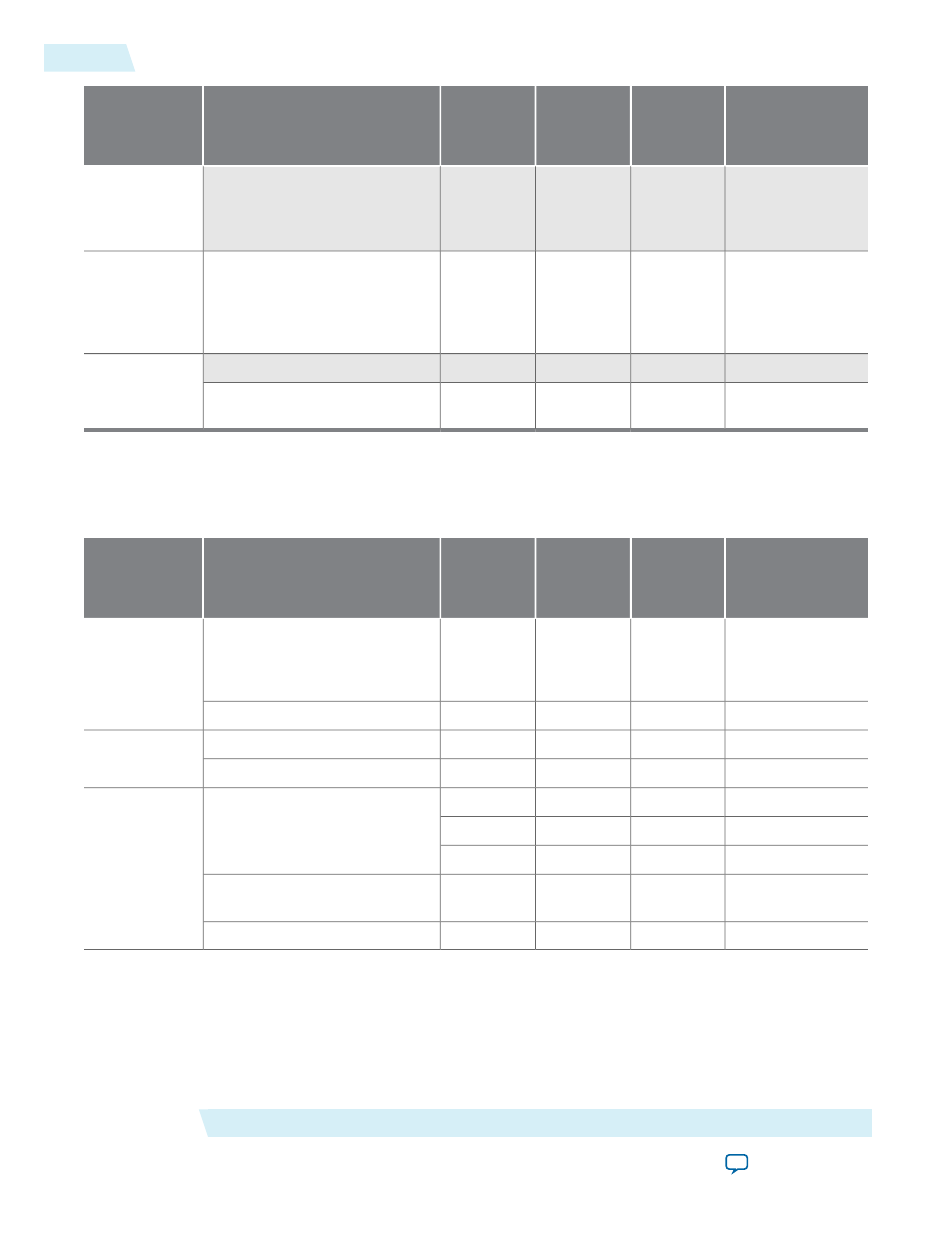

Memory

(M9K Blocks/ Mi44K

Blocks/ MLAB Bits)

Logic

Registers

Logic

Elements

FIFO Buffer

Size (Bits)

Settings

MegaCore

Function

31/0/0

3666

5614

2048x32

MII/GMII Full and half-duplex

modes supported

10/100/

1000-Mbps

Ethernet

MAC

36/0/0

10612

17017

—

MII/GMII All MAC options

enabled

Full and half-duplex modes

supported

4-port 10/

100/ 1000-

Mbps

Ethernet

MAC

0/0/0

661

1149

—

1000BASE-X

1000BASE-

X/SGMII

PCS

2/0/0

1127

2001

—

1000BASE-X SGMII bridge

enabled PMA block (GXB)

Table 1-5: Stratix V Performance and Resource Utilization

The estimated resource utilization and performance of the Triple-Speed Ethernet MegaCore function for the Stratix V

device family. The estimates are obtained by compiling the Triple-Speed Ethernet MegaCore function using the

Quartus II software targeting a Stratix V GX (5SGXMA7N3F45C3) device with speed grade -3.

Memory

(M20K Blocks/ MLAB

Bits)

Logic

Registers

Combina-

tional ALUTs

FIFO Buffer

Size (Bits)

Settings

MegaCore

Function

11/0

2018

1261

2048x32

MII

Full and half-duplex modes

supported

10/100-

Mbps Small

MAC

11/0

2018

1261

2048x32

MII All MAC options enabled

10/128

1959

1227

2048x32

GMII All MAC options enabled

1000-Mbps

Small MAC

10/128

1984

1237

2048x32

RGMII All MAC options enabled

5/2048

4298

3137

—

MII/GMII Full and half-duplex

modes supported

10/100/

1000-Mbps

Ethernet

MAC

10/2048

4971

3627

2048x8

16/2048

5145

3777

2048x32

16/768

4928

3454

2048x32

MII/GMII All MAC options

enabled

16/768

4933

3466

2048x32

RGMII All MAC options enabled

About This MegaCore Function

Altera Corporation

UG-01008

Performance and Resource Utilization

1-10

2014.06.30