Testbench verification, Testbench verification -2 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 176

• Device under test (DUT)—Your custom MegaCore function variation

• Avalon-ST Ethernet frame generator—Simulates a user application connected to the MAC system-side

interface. It generates frames on the Avalon-ST transmit interface.

• Avalon-ST Ethernet frame monitor—Simulates a user application receiving frames from the MAC system-

side interface. It monitors the Avalon-ST receive interface and decodes all data received.

• MII/RGMII/GMII Ethernet frame generator—Simulates a MAC function that sends frames to the PCS

function.

• MII/RGMII/GMII Ethernet frame monitor—Simulates a MAC function that receives frames from the

PCS function and decodes them.

• MDIO slaves—Simulates a PHY management interface. It responds to an MDIO master transactor.

• Clock and reset generator.

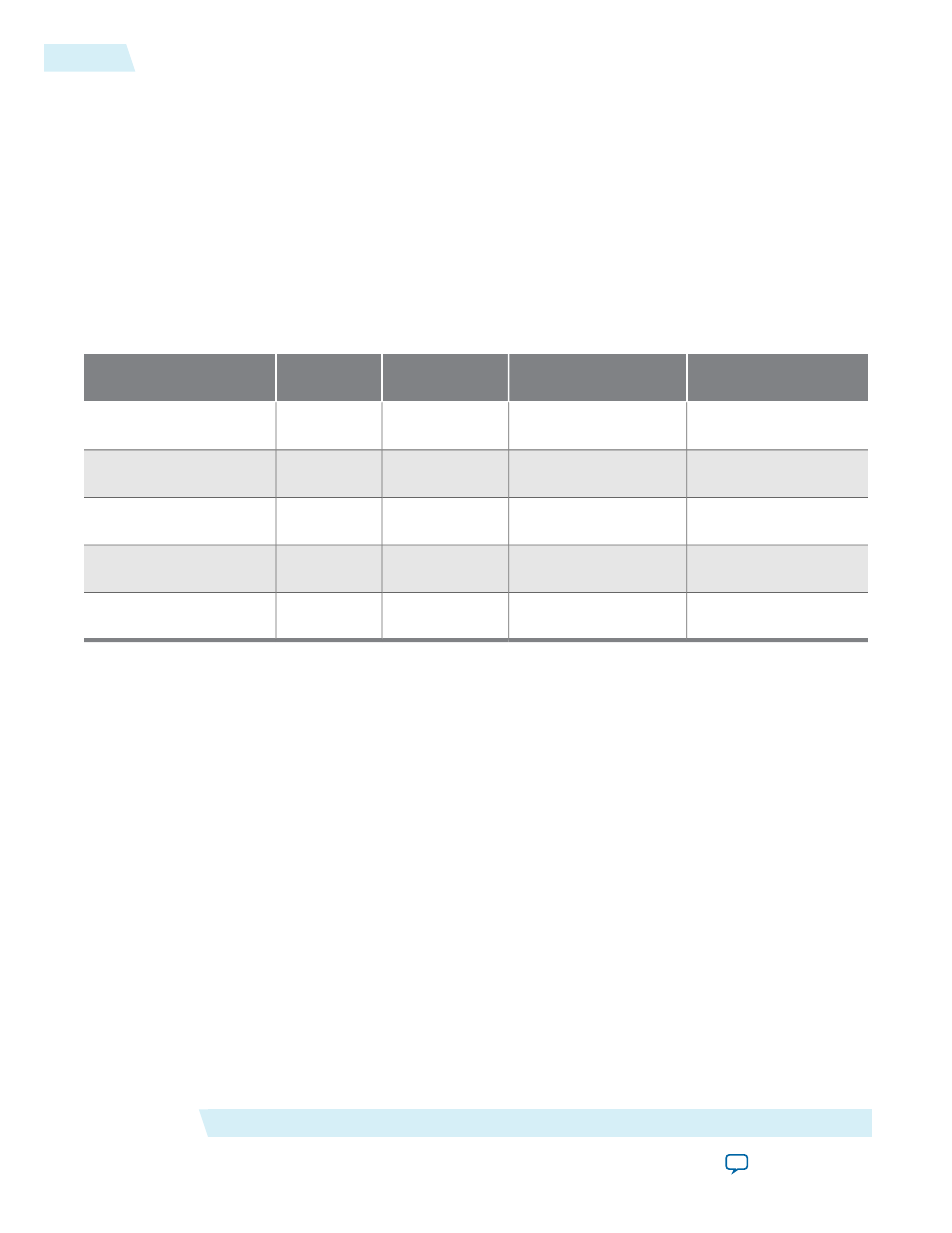

Table 10-1: Testbench Components

Frame Monitor

Frame Generator

Ethernet-Side

Interface

System-Side

Interface

Configuration

Avalon-ST Frame

Monitor

Avalon-ST Frame

Generator

GMII/MII/

RGMII

Avalon-ST

MAC only

Avalon-ST Frame

Monitor

Avalon-ST Frame

Generator

TBI

Avalon-ST

MAC with PCS

Avalon-ST Frame

Monitor

Avalon-ST Frame

Generator

1.25 Gbps

Avalon-ST

MAC with PCS and

embedded PMA

GMII/MII Frame

Monitor

GMII/MII Frame

Generator

TBI

GMII/MII

PCS only

GMII/MII Frame

Monitor

GMII/MII Frame

Generator

1.25 Gbps

GMII/MII

PCS with embedded

PMA

Testbench Verification

The testbench is self-checking and determines the success of a simulation by verifying the frames received.

It also checks for any errors detected by the frame monitors. The testbench does not verify the IEEE statistics

generated by the MAC layer. Simulation fails only if the testbench is not able to detect deliberately inserted

errors. At the end of a simulation, the testbench displays messages in the simulator console indicating its

results.

The testbench verifies the following functionality:

• Transmit and receive datapaths are functionally correct.

• Ethernet frames generated by the frame generator are received by the frame monitor.

• Additional checks for configurations that contain the MAC function:

• Correct CRC-32 is inserted.

• Short frames are padded up to at least 64 bytes in length.

• Untagged received frames of size greater than the maximum frame length are truncated to the maximum

frame length with additional bytes up to 12.

• CRC-32 is optionally discarded before the frames are received by the traffic monitor.

Testbench

Altera Corporation

UG-01008

Testbench Verification

10-2

2014.06.30