Ieee 1588v2 architecture, Ieee 1588v2 transmit datapath – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 73

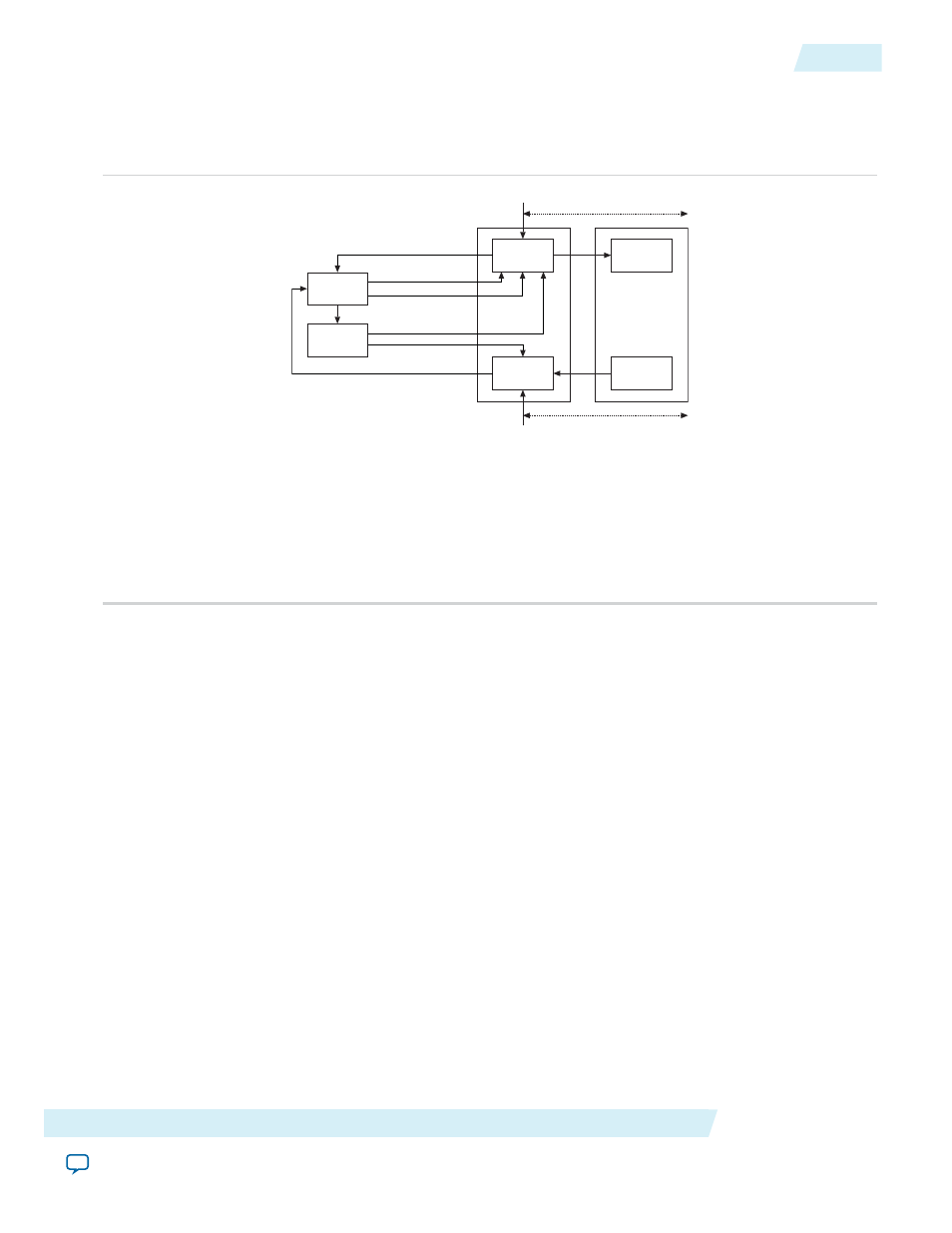

IEEE 1588v2 Architecture

Figure 4-26: Overview of the IEEE 1588v2 Feature

This figure shows only the datapaths related to the IEEE 1588v2 feature.

IEEE 1588v2

Tx Logic

IEEE 1588v2

Rx Logic

PTP Software

Stack

Time-of-Day

Clock

PHY

Tx

PHY

Rx

MAC

PHY

tx_path_delay

rx_path_delay

Timestamp &

User Fingerprint

Correction

Time of Day

Timestamp Aligned to

Receive Frame

tx_egress_timestamp_request

tx_ingress_timestamp

tx_time_of_day

rx_time_of_day

IEEE 1588v2 Transmit Datapath

The IEEE 1588v2 feature supports 1-step and 2-step clock synchronizations on the transmit datapath.

• For 1-step clock synchronization:

• Timestamp insertion depends on the PTP device and message type.

• The MAC function inserts a timestamp in the Sync PTP message if the PTP clock operates as ordinary

or boundary clock.

• Depending on the PTP device and message type, the MAC function updates the residence time in the

correction field of the PTP frame when the client asserts

tx_etstamp_ins_ctrl_residence_time_update

. The residence time is the difference between the

egress and ingress timestamps.

• For PTP frames encapsulated using the UDP/IPv6 protocol, the MAC function performs UDP

checksum correction using extended bytes in the PTP frame.

• The MAC function re-computes and re-inserts CRC-32 into the PTP frames after each timestamp or

correction field insertion.

• For 2-step clock synchronization, the MAC function returns the timestamp and the associated fingerprint

for all transmit frames when the client asserts

tx_egress_timestamp_request_valid

.

Altera Corporation

Functional Description

4-37

IEEE 1588v2 Architecture

UG-01008

2014.06.30