1000base-x/sgmii pcs with optional embedded pma – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 60

Figure 4-12: 10/100/1000 PHY Interface via MII/GMII

Altera FPGA

x5

Unused

eth_mode

set_1000

set_10

tx_clk

m_tx_d(3:0)

m_tx_en

m_tx_err

gm_tx_d(7:0)

gm_tx_en

gm_tx_err

rx_clk

m_rx_d(3:0)

m_rx_en

gm_rx_d(7:0)

gm_rx_dv

gm_rx_err

m_rx_err

en_10

25MHz

Osc

125 /25/2.5 MHz

25MHz

clk_in/xtali

25/2.5 MHz

gtx_clk

txd(7:0)

tx_en

tx_err

tx_clk

rx_clk

rxd(7:0)

rx_dv

rx_err

Clock

Driver

10/100/1000

Ethernet

MAC

10/100/1000

PHY

Optional tie to 0

if not used

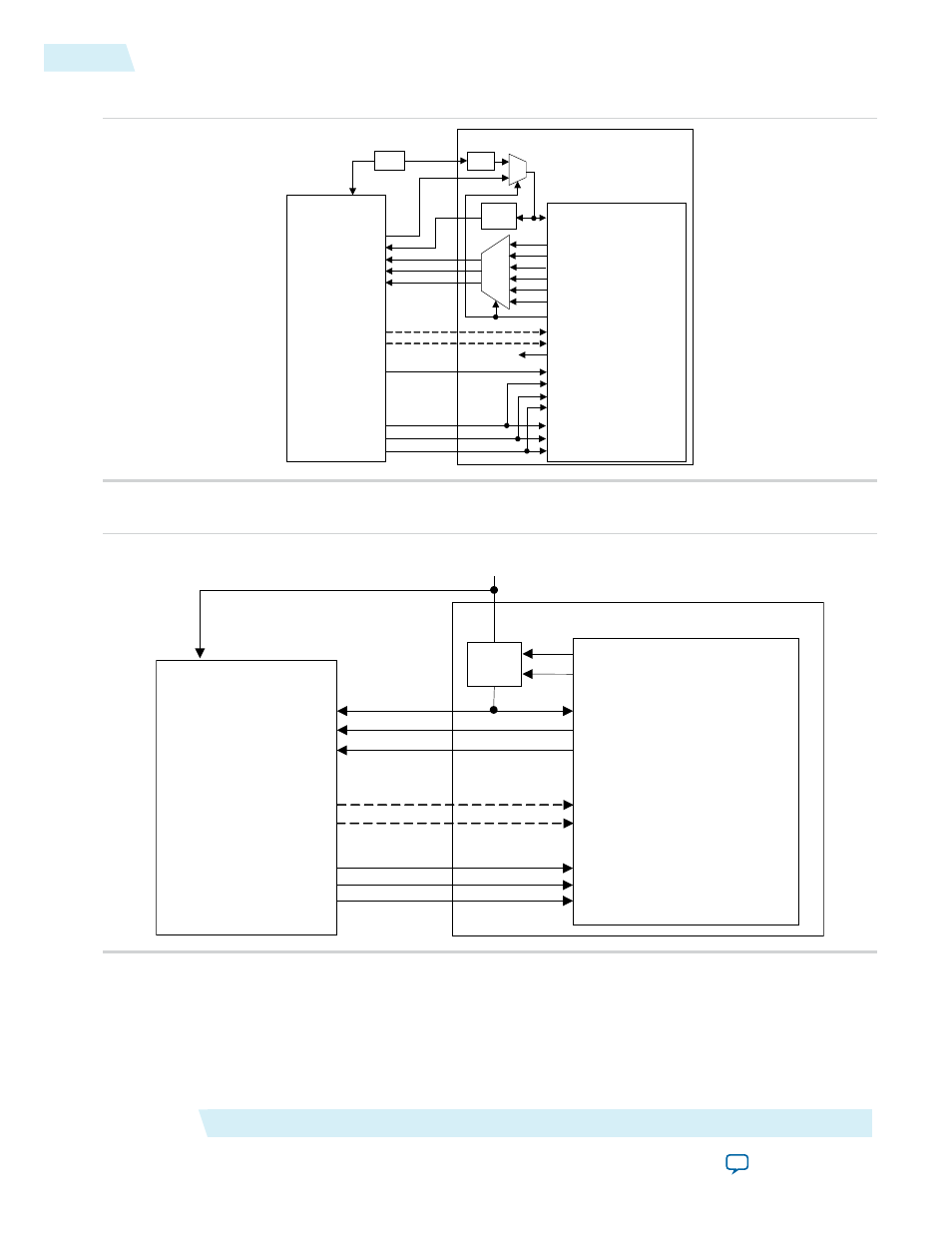

Figure 4-13: 10/100/1000 PHY Interface via RGMII

Altera FPGA

ena _10

eth _mode

set _10

set _1000

tx_clk

tx_control

rgmii _out [3:0]

rx_clk

rx_control

rgmii _in[3:0]

Reference Clock

125 MHz

gtx _clk

tx_en

txd[3:0]

rx_clk

rx_dv

rxd [3:0]

clk _in/xtali

Clock

Divider

10/100/1000

Ethernet

MAC

10/100/1000

PHY

Optional tie to 0

if not used

1000BASE-X/SGMII PCS With Optional Embedded PMA

The Altera 1000BASE-X/SGMII PCS function implements the functionality specified by IEEE 802.3 Clause

36. The PCS function is accessible via MII (SGMII) or GMII (1000BASE-X/SGMII). The PCS function

interfaces to an on- or off-chip SERDES component via the industry standard ten-bit interface (TBI).

Functional Description

Altera Corporation

UG-01008

1000BASE-X/SGMII PCS With Optional Embedded PMA

4-24

2014.06.30