Altera Triple Speed Ethernet MegaCore Function User Manual

Page 16

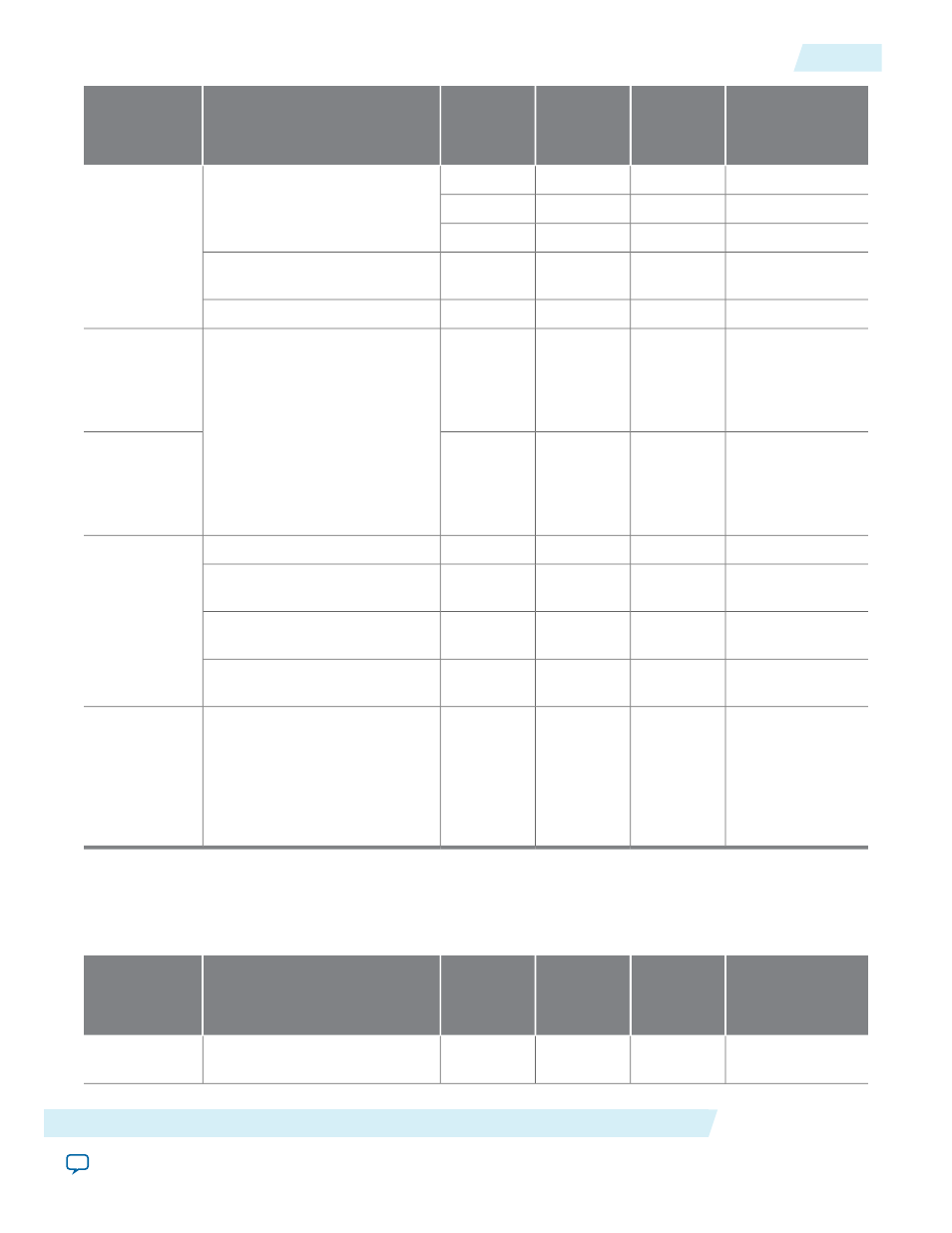

Memory

(M9K Blocks/ M144K

Blocks/MLAB Bits)

Logic

Registers

Combina-

tional ALUTs

FIFO Buffer

Size (Bits)

Settings

MegaCore

Function

0/0/3364

3395

2721

—

MII/GMII Full and half-duplex

modes supported

10/100/

1000-Mbps

Ethernet

MAC

8/0/3620

3977

3201

2048x8

12/1/3364

4425

3345

2048x32

12/1/2084

3994

3125

2048x32

MII/GMII All MAC options

enabled

12/1/2084

4021

3133

2048x32

RGMII All MAC options enabled

0/0/25008

34372

27215

—

MII/GMII All MAC options

enabled

12-port 10/

100/1000-

Mbps

Ethernet

MAC

0/0/50016

68404

54123

—

24-port 10/

100/1000-

Mbps

Ethernet

MAC

0/0/0

661

624

—

1000BASE-X

1000BASE-

X/SGMII

PCS

2/0/0

986

808

—

1000BASE-X SGMII bridge

enabled

2/0/0

1057

819

—

1000BASE-X SGMII bridge

enabled PMA block (LVDS_IO)

1/0/160

1212

1189

—

1000BASE-X SGMII bridge

enabled PMA block (GXB)

14/1/2084

4950

3971

2048×32

All MAC options enabled SGMII

bridge enabled

10/100/

1000-Mbps

Ethernet

MAC and

1000BASE-

X/SGMII

PCS

Table 1-4: Cyclone IV GX Performance and Resource Utilization

The estimated resource utilization and performance of the Triple Speed Ethernet MegaCore function for the Cyclone

IV device family. The estimates are obtained by compiling the Triple-Speed Ethernet MegaCore function using the

Quartus II software targeting a Cyclone IV GX (EP4CGX150DF27C7) device with speed grade -7.

Memory

(M9K Blocks/ Mi44K

Blocks/ MLAB Bits)

Logic

Registers

Logic

Elements

FIFO Buffer

Size (Bits)

Settings

MegaCore

Function

24/0/0

1699

2161

2048x32

RGMII Only full-duplex mode

supported

1000-Mbps

Small MAC

Altera Corporation

About This MegaCore Function

1-9

Performance and Resource Utilization

UG-01008

2014.06.30