Pause frame format, Pause frame generation – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 194

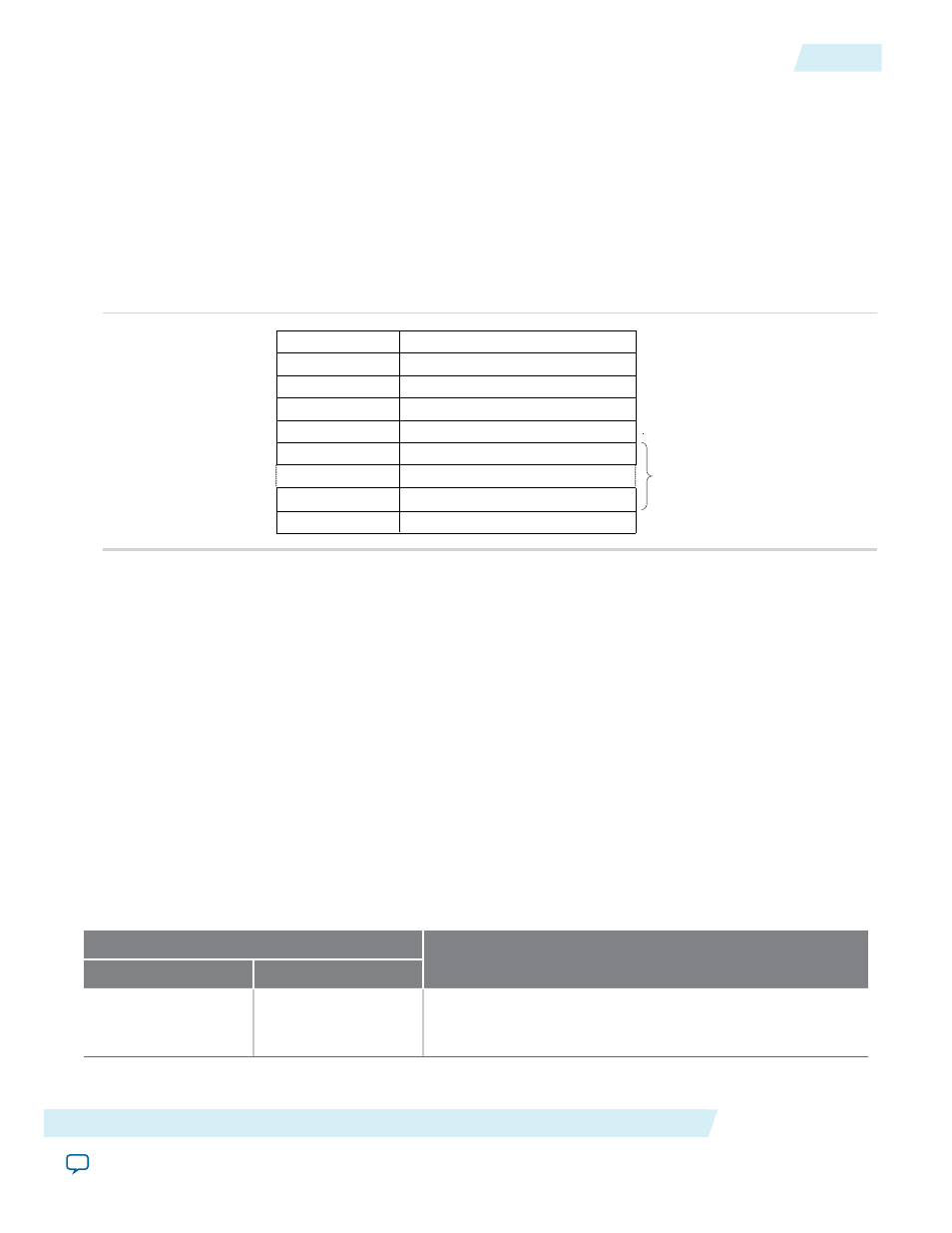

Pause Frame Format

A pause frame is generated by the receiving device to indicate congestion to the emitting device. If flow

control is supported, the emitting device should stop sending data upon receiving pause frames.

The length/type field has a fixed value of 0x8808, followed by a 2-octet opcode field of 0x0001. A 2-octet

pause quanta is defined in the second and third bytes of the frame payload (P1 and P2). The pause quanta,

P1, is the most significant byte. A pause frame has no payload length field, and is always padded with 42 bytes

of 0x00.

Figure A-4: Pause Frame Format

7octets

PREAMBLE

1 octet

SFD

6 octets

DESTINATION ADDRESS

6 octets

SOURCE ADDRESS

2 octets

42 octets

PAD

CRC

2 octets

2 octets

4 octets

Payload

PAUSE QUANTA (P1, P2)

OPCODE (0X0001)

TYPE (0x8808)

Pause Frame Generation

When you turn on the Enable full-duplex flow control option, pause frame generation is triggered by the

following events:

• RX FIFO fill level hits the

rx_section_empty

threshold.

• XOFF register write.

• XON register write.

• XOFF I/O pin (

xoff_gen

) assertion.

• XON I/O pin (

xon_gen

) assertion.

If the RX FIFO buffer is almost full, the MAC function triggers the pause frame generation to the remote

Ethernet device.

If the local Ethernet device needs to generate pause frame via XOFF or XON register write or I/O pin assertion,

it is recommended to set the

rx_section_empty

register to a larger value to avoid non-deterministic result.

summarizes the pause frame generation based on the above events.

Table A-1: Pause Frame Generation

Description

Register Write or I/O Pin Assertion

XON_GEN

XOFF_GEN

If the

XOFF_GEN

bit is set to 1, the XOFF pause frames are

continuously generated and sent to the MII/GMII TX interface

until the

XOFF_GEN

bit is cleared.

0

1

Altera Corporation

Ethernet Frame Format

A-3

Pause Frame Format

UG-01008

2014.06.30