Altera Triple Speed Ethernet MegaCore Function User Manual

Page 93

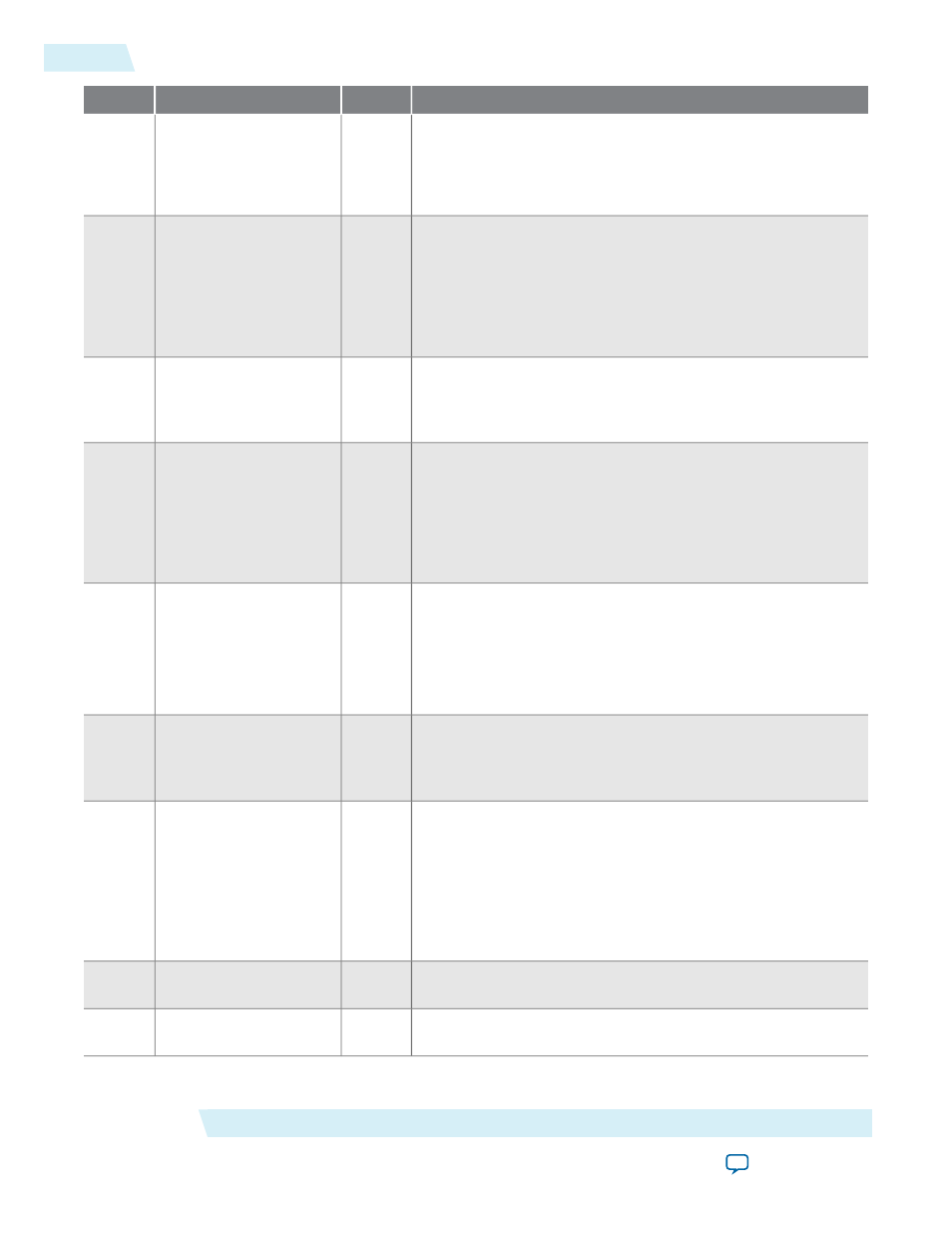

Description

R/W

Name

Bit(s)

Sleep mode enable. When the

MAGIC_ENA

bit is 1, set this bit to

1 to put the MAC function to sleep and enable magic packet

detection.

This bit is not available in the small MAC variation.

RW

SLEEP

20

Node wake-up request. Valid only when the

MAGIC_ENA

bit is

1.

• The MAC function sets this bit to 1 when a magic packet is

detected.

• The MAC function clears this bit when the

SLEEP

bit is set

to 0.

RO

WAKEUP

21

Pause frame generation. Set this bit to 1 to generate a pause

frame independent of the status of the receive FIFO buffer. The

MAC function sets the pause quanta field in the pause frame

to the value configured in the

pause_quant

register.

RW

XOFF_GEN

22

MAC control frame enable on receive.

• Set this bit to 1 to accept control frames other than pause

frames (opcode = 0x0001) and forward them to the user

application.

• Set this bit to 0 to discard control frames other than pause

frames.

RW

CNTL_FRM_ENA

23

Payload length check on receive.

• Set this bit to 0 to check the actual payload length of receive

frames against the length/type field in receive frames.

• Set this bit to 1 to omit length checking.

This bit is not available in the small MAC variation

RW

NO_LGTH_CHECK

24

10-Mbps interface enable. Set this bit to 1 to enable the 10-Mbps

interface. The MAC function asserts the

ena_10

signal when

you enable the 10-Mbps interface. You can also enable the 10-

Mbps interface by asserting the

set_10

signal.

RW

ENA_10

25

Erroneous frames processing on receive.

• Set this bit to 1 to discard erroneous frames received. This

applies only when you enable store and forward operation

in the receive FIFO buffer by setting the

rx_section_full

register to 0.

• Set this bit to 0 to forward erroneous frames to the user

application with

rx_err[0]

asserted.

RW

RX_ERR_DISC

26

Set this bit to 1 to disable MAC configuration register read

timeout.

RW

DISABLE_READ_ TIMEOUT

27

—

—

Reserved

28 –

30

Configuration Register Space

Altera Corporation

UG-01008

Command_Config Register (Dword Offset 0x02)

6-10

2014.06.30