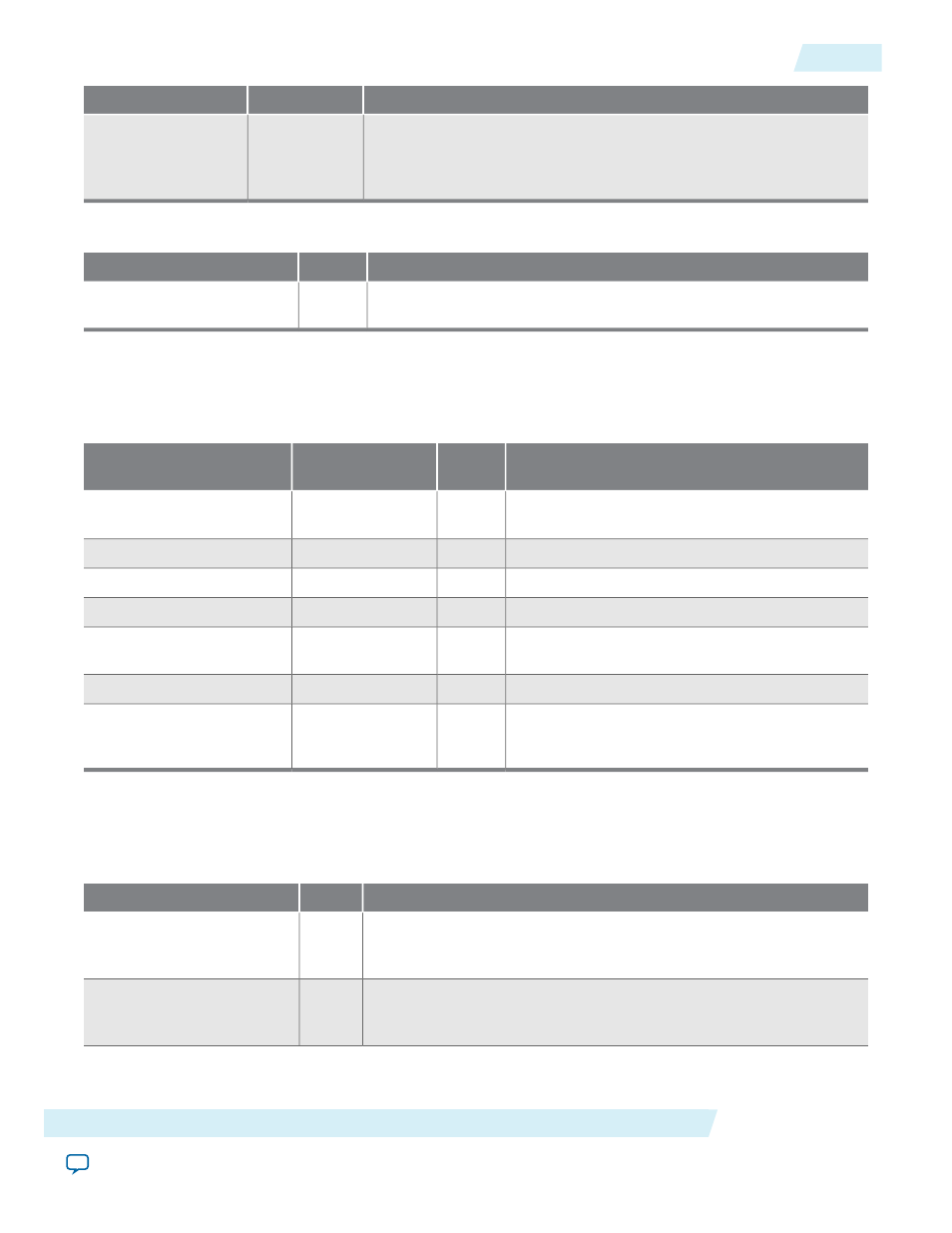

Mac control interface signals, Mac status signals – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 118

Description

I/O

Name

GMII /RGMII/ MII receive clock. Provides the timing reference for

all rx related signals. The values of

gm_rx_d[7:0]

,

gm_rx_dv

,

gm_rx_

err

, and of

m_rx_d[3:0]

,

m_rx_en, m_rx_err

are valid on the rising

edge of

rx_clk

.

I

rx_clk

Table 7-2: Reset Signal

Description

I/O

Name

Assert this signal to reset all logic in the MAC and PCS control

interface. The signal must be asserted for at least three clock cycles.

I

reset

MAC Control Interface Signals

The MAC control interface is an Avalon-MM slave port that provides access to the register space.

Table 7-3: MAC Control Interface Signals

Description

I/O

Avalon-MM Signal

Type

Name

Register access reference clock. Set the signal to

a value less than or equal to 125 MHz.

I

clk

clk

Register write enable.

I

write

reg_wr

Register read enable.

I

read

reg_rd

32-bit word-aligned register address.

I

address

reg_addr[7:0]

Register write data. Bit 0 is the least significant

bit.

I

writedata

reg_data_in[31:0]

Register read data. Bit 0 is the least significant bit.

O

readdata

reg_data_out[31:0]

Register interface busy. Asserted during register

read or register write access; deasserted when the

current register access completes.

O

waitrequest

reg_busy

MAC Status Signals

The MAC status signals which allow you to set the transfer mode of the Ethernet-side interface.

Table 7-4: MAC Status Signals

Description

I/O

Name

Ethernet mode. This signal is set to 1 when the MAC function is

configured to operate at 1000 Mbps; set to 0 when it is configured to

operate at 10/100 Mbps.

O

eth_mode

10 Mbps enable. This signal is set to 1 to indicate that the PHY interface

should operate at 10 Mbps. Valid only when the

eth_mode

signal is set

to 0.

O

ena_10

Altera Corporation

Interface Signals

7-3

MAC Control Interface Signals

UG-01008

2014.06.30