Altera Triple Speed Ethernet MegaCore Function User Manual

Page 122

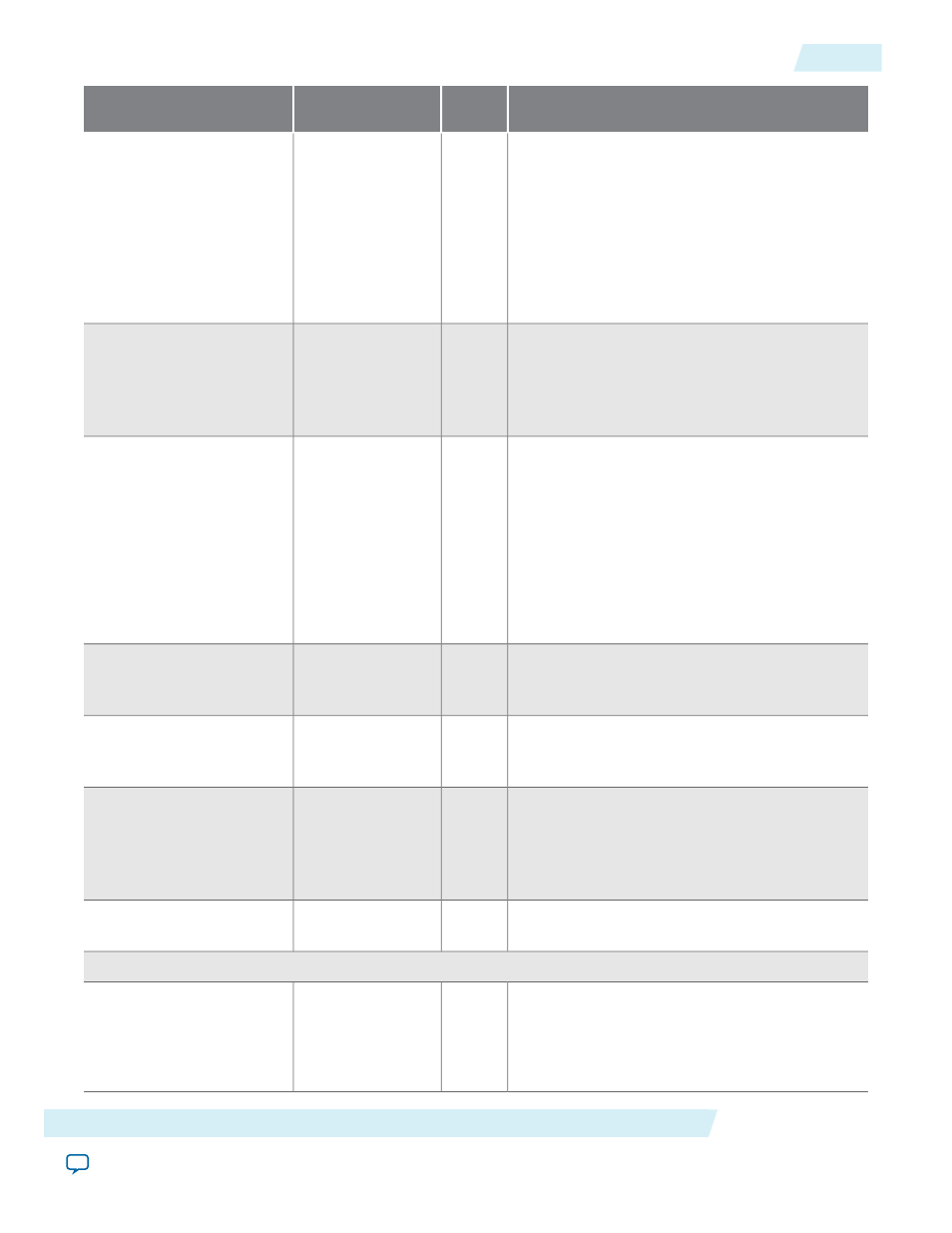

Description

I/O

Avalon-ST Signal

Type

Name

Transmit data write enable. Assert this signal to

indicate that the data on the following signals are

valid:

ff_tx_data[(DATAWIDTH-1):0]

,

ff_tx_

sop

, and

ff_tx_eop

.

In cut-through mode, keep this signal asserted

throughout the frame transmission. Otherwise,

the frame is truncated and forwarded to the

Ethernet-side interface with an error.

I

valid

ff_tx_wren

Transmit data.

DATAWIDTH

can be either 8 or 32

depending on the FIFO data width configured.

When

DATAWIDTH

is 32, the first byte transmitted

is

ff_tx_data[31:24]

followed by

ff_tx_

data[23:16]

and so forth.

I

data

ff_tx_data

[(DATAWIDTH-1):0]

Transmit data modulo. Indicates invalid bytes in

the final frame word:

• 11:

ff_tx_data[23:0]

is not valid

• 10:

ff_tx_data[15:0]

is not valid

• 01:

ff_tx_data[7:0]

is not valid

• 00:

ff_tx_data[31:0]

is valid

This signal applies only when

DATAWIDTH

is set

to 32.

I

empty

ff_tx_mod[1:0]

Transmit start of packet. Assert this signal when

the first byte in the frame (the first byte of the

destination address) is driven on

ff_tx_data

.

I

startofpacket

ff_tx_sop

Transmit end of packet. Assert this signal when

the last byte in the frame (the last byte of the FCS

field) is driven on

ff_tx_data

.

I

endofpacket

ff_tx_eop

Transmit frame error. Assert this signal with the

final byte in the frame to indicate that the

transmit frame is invalid. The MAC function

forwards the invalid frame to the GMII with an

error.

I

error

ff_tx_err

MAC ready. When asserted, the MAC function

is ready to accept data from the user application.

O

ready

ff_tx_rdy

Component-Specific Signals

Transmit CRC insertion. Set this signal to 0 when

ff_tx_eop

is set to 1 to instruct the MAC

function to compute a CRC and insert it into the

frame. If this signal is set to 1, the user application

is expected to provide the CRC.

I

—

ff_tx_crc_fwd

Altera Corporation

Interface Signals

7-7

MAC Transmit Interface Signals

UG-01008

2014.06.30