Table 7-24: references – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 135

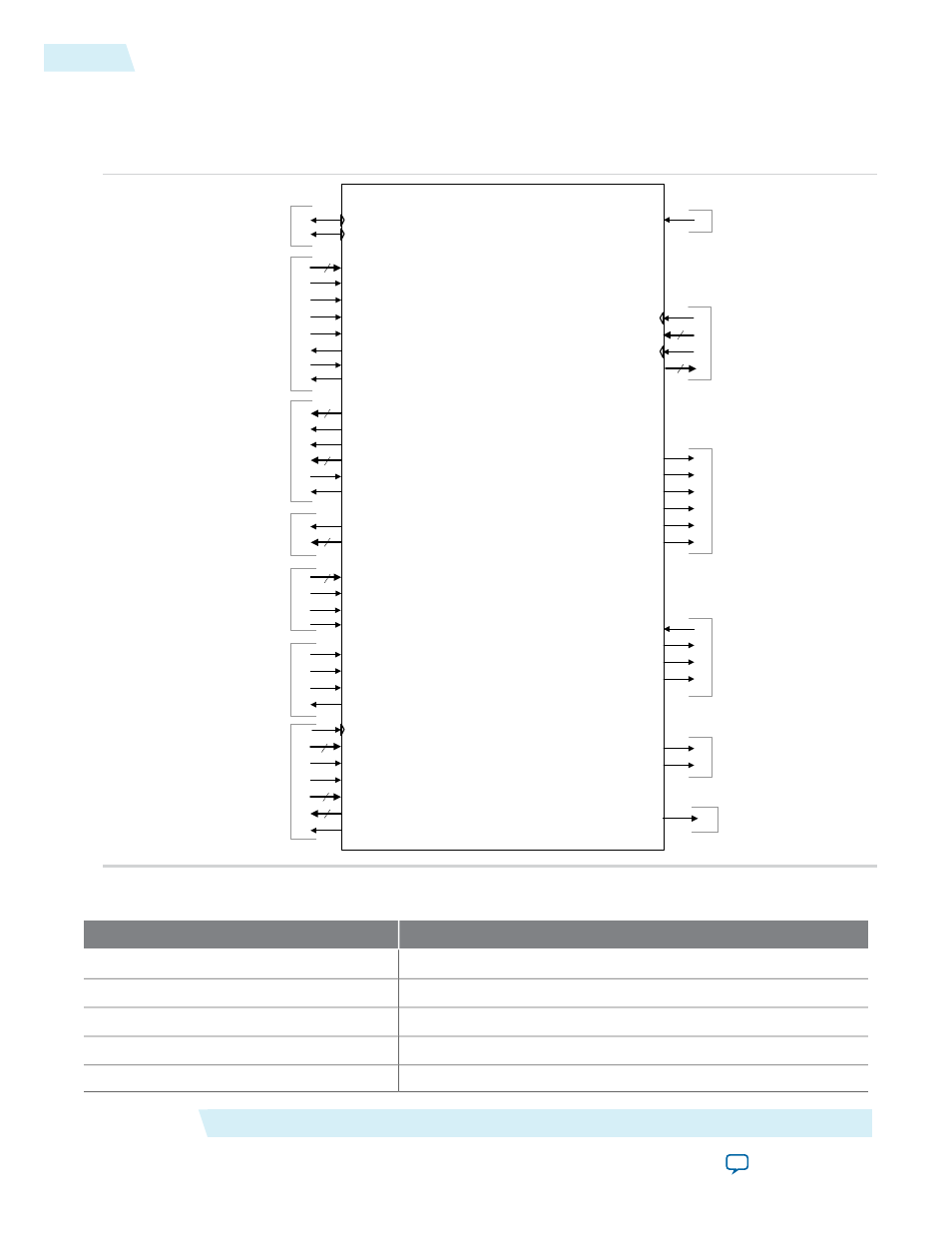

10/100/1000 Multiport Ethernet MAC with 1000BASE-X/SGMII PCS Signals

Figure 7-4: 10/100/1000 Multiport Ethernet MAC Function without Internal FIFO Buffers with

1000BASE-X/SGMII PCS Signals

PHY

Management

Signals

mdio _in

mdc

mdio _oen

mdio _out

Reset

Signal

reset

Status

LED

Signals

led_an _n

led_crs _n

led_col _n

led_char _err_n

led_link_n

led_disp _err_n

SERDES

Control

Signals

sd _loopback _n

powerdown _n

Pause and Magic

Packet Signals

xon _gen _n

xoff_gen _n

magic _wakeup _n

magic _sleep _n_n

8

5

mac _tx_clk _n

mac _rx_clk _n

Clock

Signals

data _rx_data _n[7:0]

data _rx_eop _n

data _rx_sop _n

data _rx_error _n[4:0]

data _rx_ready _n

data _rx_valid _n

MAC Receive

Interface Signals

MAC Transmit

Interface Signals

data _tx_data _n[7:0]

data _tx_eop _n

data _tx_error _n

data _tx_sop _n

data _tx_valid _n

data _tx_ready _n

tx_crc _fwd_n

tx_ff_uflow_n

8

MAC Packet

Classification

Signals

pkt_class _valid _n

pkt_class _data _n[4:0]

5

n

rx_afull_data [1:0]

rx_afull_valid

MAC FIFO

Status Signals

rx_afull_clk

Ten Bit

Interface

Signals

tbi_rx_clk _n

tbi_rx_d_n[9:0]

tbi_tx_clk _n

tbi_tx_d_n[9:0]

10

10

32

32

MAC Control

Interface

Signals

clk

reg _rd

reg _wr

reg _data _out[31:0]

reg _data _in[31:0]

reg _busy

8

rx_afull_channel[CHANNEL_WIDTH-1:0]

reg_addr[(log2 MAX_CHANNELS+7):0][7:0]

ECC Status

Signal

pcs_eccstatus[1:0]

Multi-Port MAC with 1000BASE-X/SGMII PCS

Table 7-24: References

Section

Interface Signal

on page 7-2

Clock and reset signals

on page 7-3

MAC control interface

MAC Transmit Interface Signals

on page 7-6

MAC transmit interface

on page 7-4

MAC receive interface

Multiport MAC Packet Classification Signals

on page 7-14

MAC packet classification signals

Interface Signals

Altera Corporation

UG-01008

10/100/1000 Multiport Ethernet MAC with 1000BASE-X/SGMII PCS Signals

7-20

2014.06.30