Altera Triple Speed Ethernet MegaCore Function User Manual

Page 92

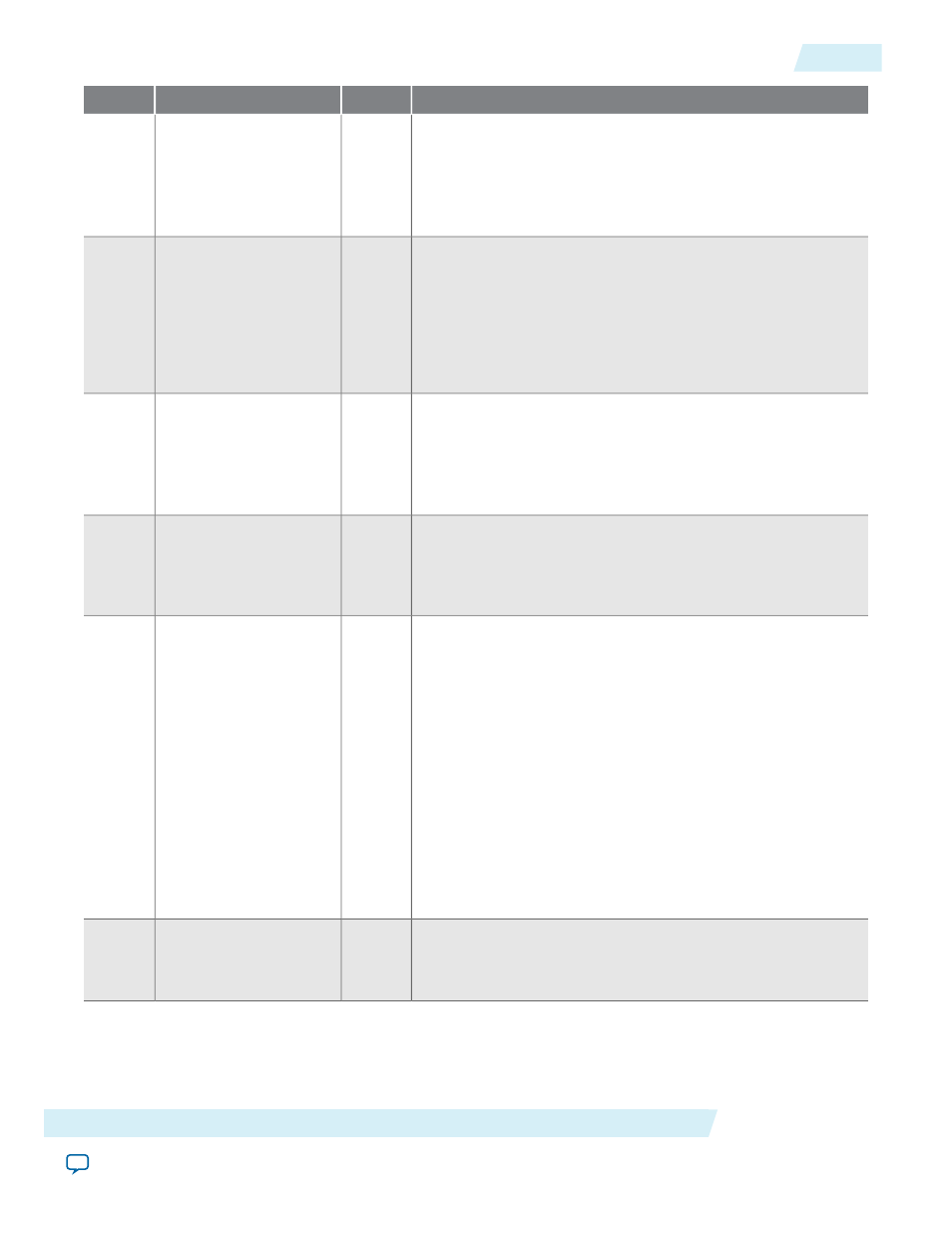

Description

R/W

Name

Bit(s)

Late collision condition.

• The MAC function sets this bit to 1 when it detects a

collision after transmitting 64 bytes and discards the frame.

• The MAC function clears this bit following a hardware or

software reset. See the

SW_RESET

bit description.

RO

LATE_COL

12

Software reset. Set this bit to 1 to trigger a software reset. The

MAC function clears this bit when it completes the software

reset sequence.

When reset is triggered, the MAC function completes the

current transmission or reception, and subsequently disables

the transmit and receive logic, flushes the receive FIFO buffer,

and resets the statistics counters.

RW

SW_RESET

13

Hash-code mode selection for multicast address resolution.

• Set this bit to 0 to generate the hash code from the full 48-

bit destination address.

• Set this bit to 1 to generate the hash code from the lower 24

bits of the destination MAC address.

RW

MHASH_SEL

14

Local loopback enable. Set this bit to 1 to enable local loopback

on the RGMII/GMII/MII of the MAC. The MAC function sends

transmit frames back to the receive path.

This bit is not available in the small MAC variation.

RW

LOOP_ENA

15

Source MAC address selection on transmit. If you set the

TX_

ADDR_INS

bit to 1, the value of these bits determines the MAC

address the MAC function selects to overwrite the source MAC

address in frames received from the user application.

• 000 = primary address configured in the

mac_0

and

mac_1

registers.

• 100 = supplementary address configured in the

smac_0_0

and

smac_0_1

registers.

• 101 = supplementary address configured in the

smac_1_0

and

smac_1_1

registers.

• 110 = supplementary address configured in the

smac_2_0

and

smac_2_1

registers.

• 111 = supplementary address configured in the

smac_3_0

and

smac_3_1

registers.

RW

TX_ADDR_SEL

[2:0]

18 –

16

Magic packet detection. Set this bit to 1 to enable magic packet

detection.

This bit is not available in the small MAC variation.

RW

MAGIC_ENA

19

Altera Corporation

Configuration Register Space

6-9

Command_Config Register (Dword Offset 0x02)

UG-01008

2014.06.30