Pcs configuration register space, Pcs configuration register space -18, Configuration register space – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 101

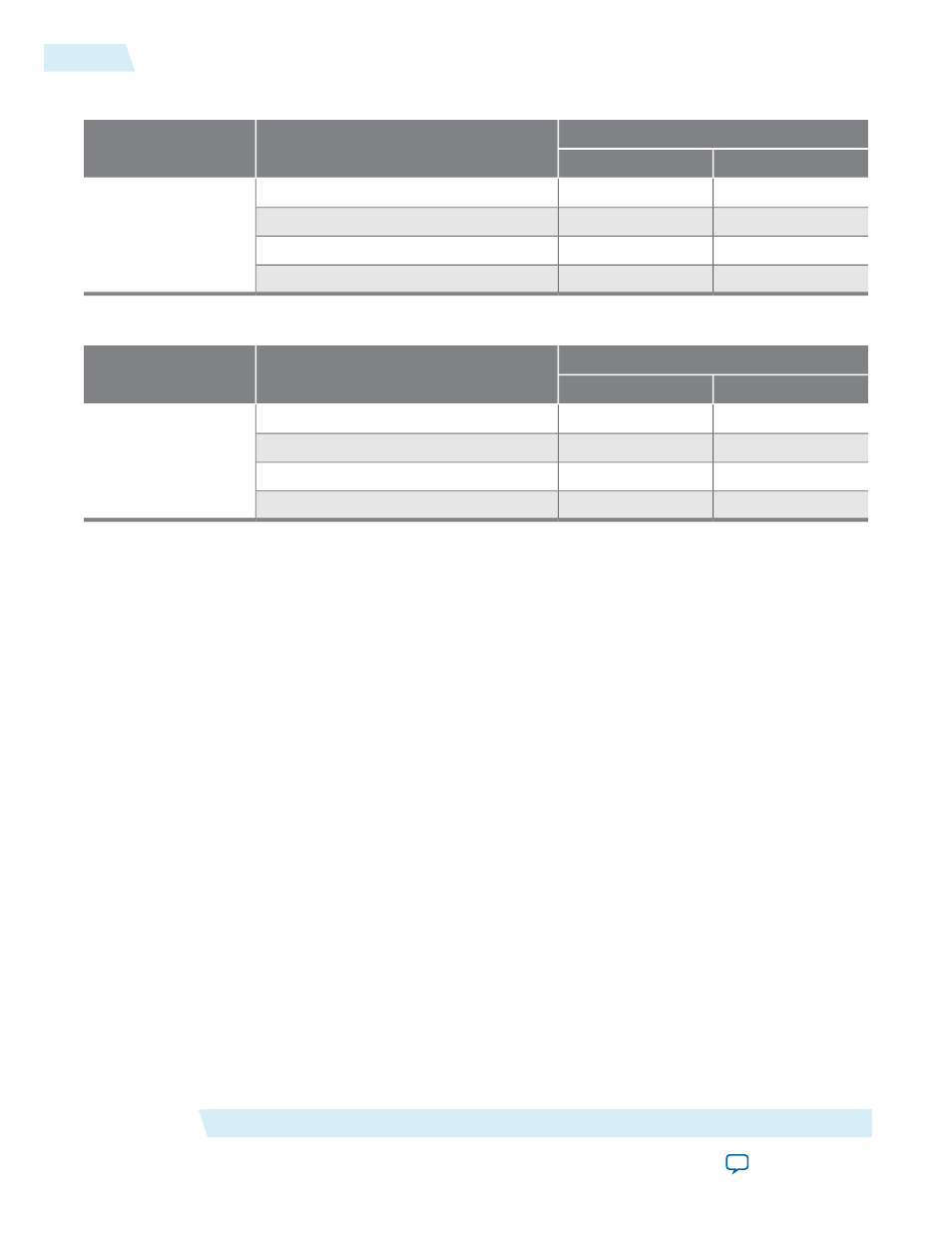

Table 6-10: IEEE 1588v2 Feature PMA Delay—Simulation Model

Timing Adjustment

Device

Delay

RX register

TX register

33.5 UI

11 UI

Stratix V or Arria V GZ

Digital

23.5 UI

10 UI

Arria V GX, Arria V GT, or Arria V SoC

23.5 UI

32 UI

Arria 10

23.5 UI

10 UI

Cyclone V GX or Cyclone V SoC

Table 6-11: IEEE 1588v2 Feature LVDS I/O Delay—Simulation Model

Timing Adjustment

Device

Delay

RX register

TX register

26 UI

19.5 UI

Stratix V or Arria V GZ

Digital

26 UI

19.5 UI

Arria V GX, Arria V GT, or Arria V SoC

24.5 UI

19.5 UI

Arria 10

26 UI

19.5 UI

Cyclone V GX or Cyclone V SoC

PCS Configuration Register Space

This section describes the PCS registers. Use the registers to configure the PCS function or retrieve its status.

In MAC and PCS variations, the PCS registers occupy the MAC register space and you access these

registers via the MAC 32-bit Avalon-MM control interface. PCS registers are 16 bits wide, they

Note:

therefore occupy only the lower 16 bits and the upper 16 bits are set to 0. The offset of the first PCS

register in this variation is mapped to dword offset 0x80.

If you instantiate the IP core using the MegaWizard Plug-in Manager flow, use word addressing to access

the register spaces. When you instantiate MAC and PCS variations, map the PCS registers to the respective

dword offsets in the MAC register space by adding the PCS word offset to the offset of the first PCS. For

example,

• In PCS only variation, you can access the

if_mode

register at word offset 0x14.

• In MAC and PCS variations, map the

if_mode

register to the MAC register space:

• Offset of the first PCS register = 0x80

•

if_mode

word offset = 0x14

•

if_mode

dword offset = 0x80 + 0x14 = 0x94

If you instantiate the MAC and PCS variation using the Qsys system, access the register spaces using byte

addressing. Convert the dword offsets to byte offsets by multiplying the dword offsets by 4. For example,

• For MAC registers:

•

comand_config

dword offset = 0x02

•

comand_config

byte offset = 0x02 × 4 = 0x08

Configuration Register Space

Altera Corporation

UG-01008

PCS Configuration Register Space

6-18

2014.06.30