Rgmii transmit, Rgmii receive, Rgmii transmit -42 – Altera Triple Speed Ethernet MegaCore Function User Manual

Page 157: Rgmii receive -42, The rgmii control signal, Bus. between frames, Figure 7-17: rgmii transmit in gigabit mode, Asserted with, Error signal (at the falling edge of

RGMII Transmit

On transmit, all data transfers are synchronous to both edges of

tx_clk

. The RGMII control signal

tx_control

is asserted to indicate the start of a new frame and remains asserted until the last upper nibble of the frame

is present on the

rgmii_out[3:0]

bus. Between frames,

tx_control

remains deasserted.

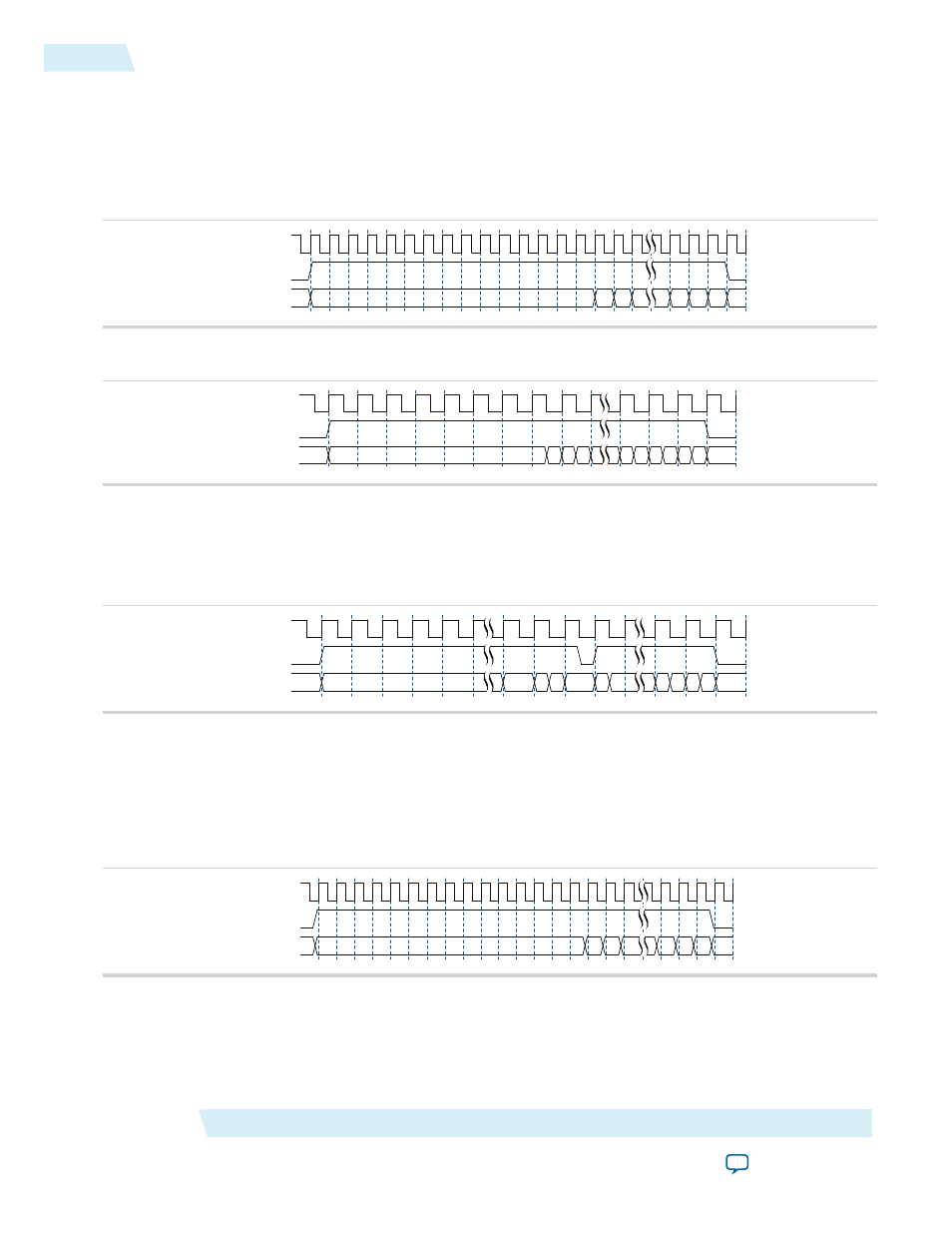

Figure 7-16: RGMII Transmit in 10/100 Mbps

tx_clk

tx_control

rgmii_out[3:0]

00

5

D

0

5

1

6

1

9

1

Figure 7-17: RGMII Transmit in Gigabit Mode

tx_clk

tx_control

rgmii_out[3:0]

00

5

D

0

5

4

5

E

5

F

5

0

6

0

If a frame is received on the Avalon-ST interface with an error (

ff_tx_err

asserted with

ff_tx_eop

), the

frame is subsequently transmitted with the RGMII

tx_control

error signal (at the falling edge of

tx_clk

)

at any time during the frame transfer.

Figure 7-18: RGMII Transmit with Error in 1000 Mbps

tx_clk

tx_control

rgmii_out[3:0]

00

5

0

4

6

0

1

0

0

8

0

9

0

RGMII Receive

On receive all signals are sampled on both edges of

rx_clk

. The RGMII control signal

rx_control

is asserted

by the PHY to indicate the start of a new frame and remains asserted until the last upper nibble of the frame

is present on

rgmii_in[3:0]

bus. Between frames,

rx_control

remains deasserted.

Figure 7-19: RGMII Receive in 10/100 Mbps

rx_clk

rx_control

rgmii_in[3:0]

00

5

D

0

5

1

6

1

9

0

Interface Signals

Altera Corporation

UG-01008

RGMII Transmit

7-42

2014.06.30