Altera Triple Speed Ethernet MegaCore Function User Manual

Page 89

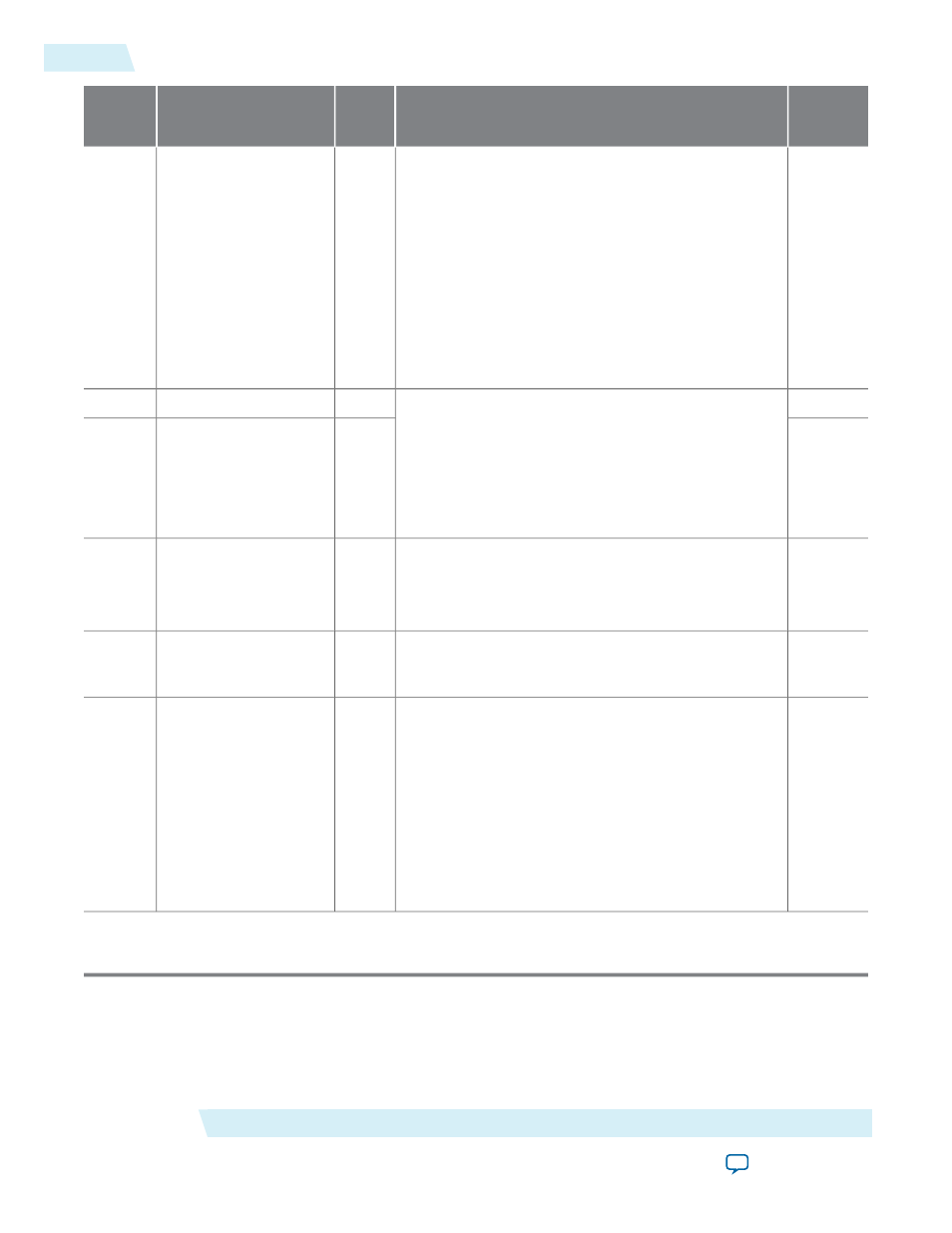

HW Reset

Description

R/W

Name

Dword

Offset

0

Variable-length almost-full threshold of the transmit

FIFO buffer. Use the depth of your FIFO buffer to

determine this threshold.

You must set this register to a value greater than or equal

to 3. A value of 3 indicates 0 ready latency; a value of 4

indicates 1 ready latency, and so forth. Because the

maximum ready latency on the Avalon-ST interface is 8,

you can only set this register to a maximum value of 11.

This threshold is typically set to 3.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the register is set to a fixed value of 3.

RW/

RO

tx_almost_full

0x0E

0

• Bits[4:0]—5-bit PHY address. Set these registers to

the addresses of any connected PHY devices you want

to access. The

mdio_addr0

and

mdio_addr1

registers

contain the addresses of the PHY whose registers are

mapped to MDIO Space 0 and MDIO Space 1

respectively.

• Bits[31:5]—unused. Set to read-only value of 0.

RW

mdio_addr0

0x0F

1

RW

mdio_addr1

0x10

0xFFFF

• Bit[15:0]—16-bit holdoff quanta. When you enable

the flow control, use this register to specify the gap

between consecutive XOFF requests.

• Bits[31:16]—unused.

RW

holdoff_quant

0x11

0

—

—

Reserved

0x12

–

0x16

0

• Bits[4:0]—minimum IPG. Valid values are between

8 and 26 byte-times. If this register is set to an invalid

value, the MAC still maintains a typical minimum

IPG value of 12 bytes between packets, although a read

back to the register reflects the invalid value written.

In 10/100 and 1000 Small MAC core variations, this

register is RO and the register is set to a fixed value

of 12.

Bits[31:5]—unused. Set to read-only value 0.

RW

tx_ipg_length

0x17

Note to

:

1. Register is not available in 10/100 and 1000 Small MAC variations.

Configuration Register Space

Altera Corporation

UG-01008

Base Configuration Registers (Dword Offset 0x00 – 0x17)

6-6

2014.06.30