6 transmitting data, 7 .1 .6 transmitting data -4, Figure 7-2 . slave i – Maxim Integrated MAX31782 User Manual

Page 60: C data flow -4, 6transmittingdata

MaximIntegrated 7-4

MAX31782 User’s Guide

Revision 0; 8/11

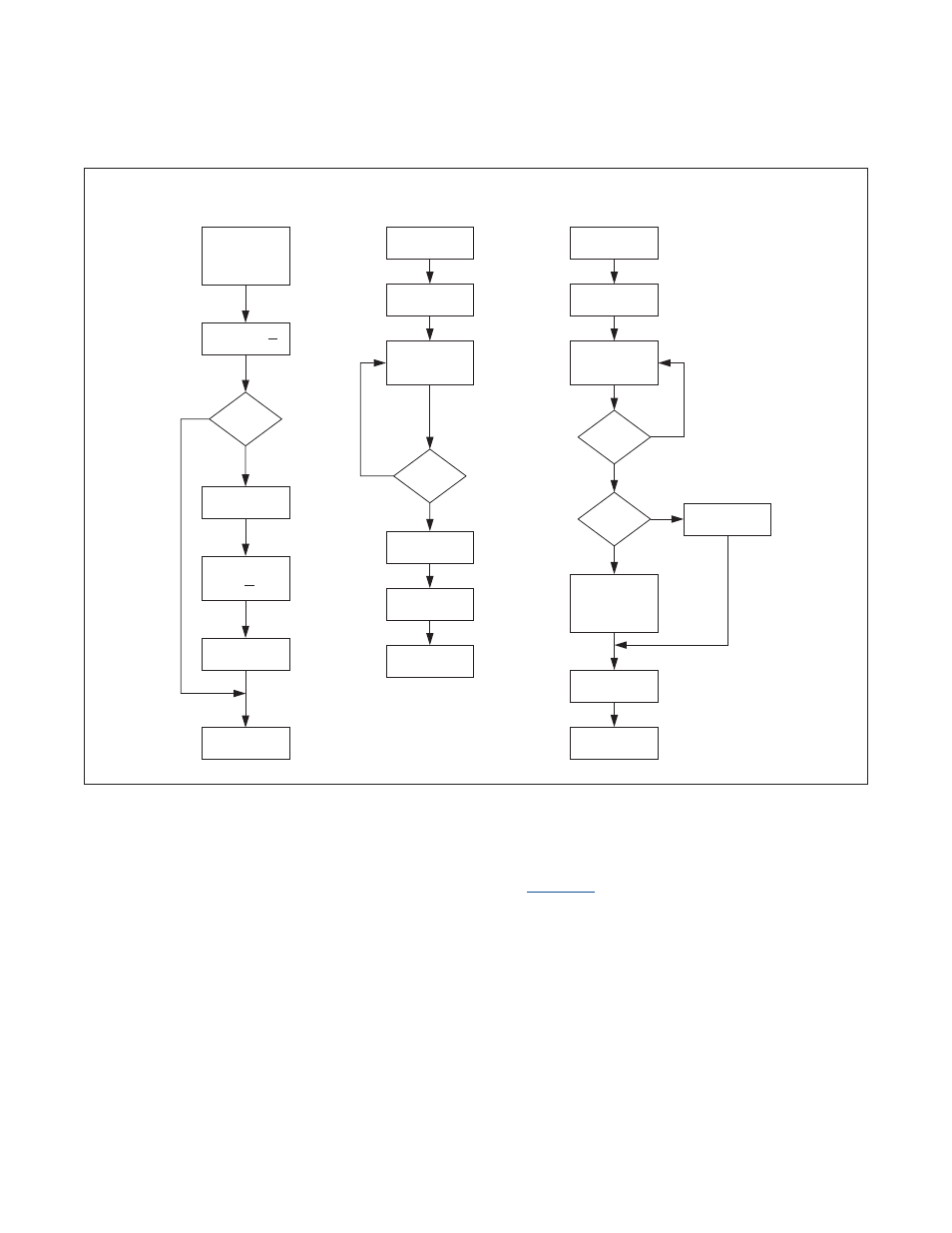

7.1.6TransmittingData

The MAX31782 I

2

C slave controller enters into data transmission mode after receiving a matching slave address with

the R/W bit set to a 1 . The steps of data transmission are shown in

. Data transmission is started by software

loading a byte of data into the I2CBUF_S register . Loading I2CBUF_S causes the I2CBUSY bit in I2CST_S to be set .

Once set, a write to I2CBUF_S is ignored . The first bit of data (most significant bit) is shifted to SDA when SCL is low .

Each of the next 7 bits is then shifted following high-to-low transitions of SCL .

Following the 8th data (least significant bit) being shifted to SDA, the SDA line is released by the MAX31782 slave

controller . This allows the host to signal an ACK or NACK during the 9th clock cycle . The MAX31782 I

2

C slave control-

ler samples the acknowledge bit following the rising 9th SCL rising edge . After the acknowledge bit is sampled, the

MAX31782 I

2

C slave controller performs the following tasks:

• Sets the I2CST_S .I2CTXI flag to indicate that the I

2

C slave controller transmit a complete byte . This can generate an

interrupt if enabled .

• Sets or clears the I2CST_S .I2CNACKI flag to reflect the received acknowledge bit . The setting of I2CNACKI can

generate and interrupt if enabled .

Figure 7-2. Slave I

2

C Data Flow

DETECT START

I2CSRI = 1

I2CBUS = 1

I2CBUSY = 1

RECEIVING SLAVE

ADDRESS

RECEIVE

Addr[6:0] + R/W

TRANSMIT

I2CACK

MATCH

I2CSLA_S?

Y

N

I2CAMI = 1

I2CBUSY = 0

SET I2CMODE

ACCORDING TO

R/W

TRANSMITTING

BYTE

I2CBUSY = 1

I2CROI = 1

WRITE TO

I2CBUF_S

RECEIVING

BYTE

DETECT FIRST SCL

RISING EDGE

RECEIVE

ACKNOWLEDGE

8 BITS

TRANSMIT?

Y

N

N

I2CTXI = 1

I2CBUSY = 0

TRANSMIT SHIFT

REGISTER BYTE,

MSB FIRST

I2CNACKI =

ACKNOWLEDGE

I2CBUSY = 1

SEND

I2CACK

I2CBUSY = 0

RECEIVE A BIT INTO

SHIFT REGISTER,

MSB FIRST

LOAD SHIFT

REGISTER INTO

I2CBUF_S

I2CRXI = 1

8 BITS

RECEIVED?

Y

RECEIVER

FULL?

Y

N