4 in-circuit debug flag register (icdf, m2[1bh]), 5 in-circuit debug buffer register (icdb, m2[1ch]), 5in-circuitdebugbufferregister(icdb,m2[1ch]) – Maxim Integrated MAX31782 User Manual

Page 150: 4in-circuitdebugflagregister(icdf,m2[1bh])

MaximIntegrated 17-15

MAX31782 User’s Guide

Revision 0; 8/11

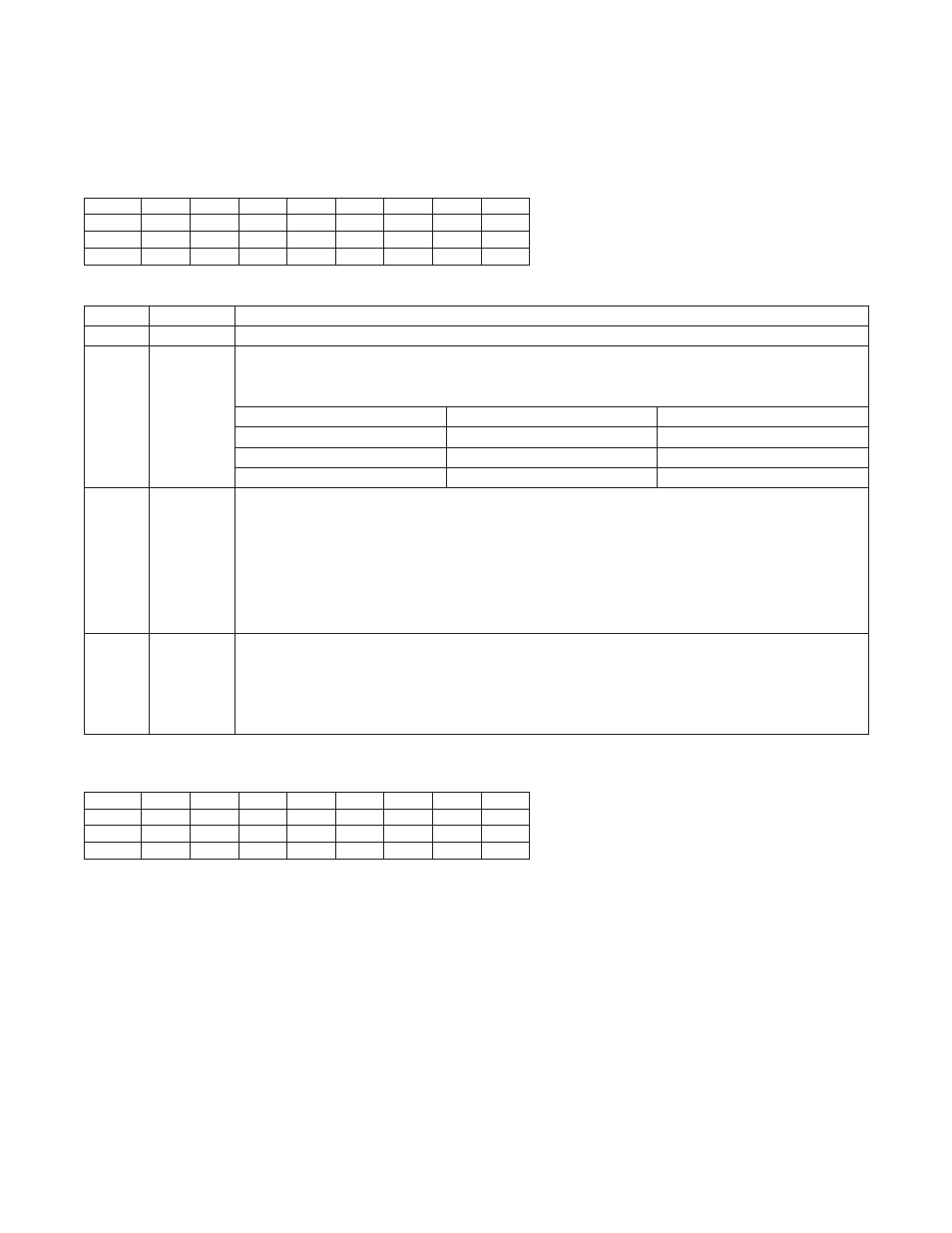

17.3.5In-CircuitDebugBufferRegister(ICDB,M2[1Ch])

This register serves as the parallel holding buffer for the debug shift register of the TAP . Data is read from or written to

ICDB for serial communication between the debug routines and the external host .

r = read, s = special

17.3.4In-CircuitDebugFlagRegister(ICDF,M2[1Bh])

Bit

7

6

5

4

3

2

1

0

Name

-

-

-

-

PSS1

PSS0

JTAG_SPE

TXC

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

rw

rw

rw

rw

Bit

7

6

5

4

3

2

1

0

Name

ICDB .7

ICDB .6

ICDB .5

ICDB .4

ICDB .3

ICDB .2

ICDB .1

ICDB .0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

7:4

Reserved

Reserved . Do not write to these bits .

3:2

PSS[1:0]

Programming Source Select Bits [1:0] . These bits are used to select a programming interface during

In-System programming when JTAG_SPE is set to 1, otherwise, the logic values of these bits have no

meaning:

PSS1

PSS0

Interface/Action

0

0

JTAG

0

1

I2C

1

x

Exit Loader

1

JTAG_SPE

System Program Enable . The JTAG_SPE bit is used for In-System programming support and its logical

state, when read by the CPU, always reflects the logical-OR of the JTAG_SPE bit that is write accessible

by the CPU and the SPE bit of the System Programming Buffer (SPB) Register in the TAP Module (which

is accessible via JTAG) . The logical state of this bit determines the program flow after a reset . When it is

set to logic 1, In-System programming will be executed by the Utility ROM . When it is cleared to 0, execu-

tion will be transferred to user code . This bit allows read/write access by the CPU and is cleared to 0 only

on a power-on reset or Test-Logic-Reset . The JTAG SPE bit will be cleared by hardware when the ROD

bit is set . CPU writes to the JTAG_SPE bit (0 or 1) will result in clearing of the PSS[1:0] bits .

0

TXC

Serial Transfer Complete . This bit is set by hardware at the end of a transfer cycle at the TAP commu-

nication link . The TXC bit helps the debug engine to recognize host requests, either command or data .

This bit is normally set by ROM code to signify or request the sending or receiving of data . The TXC bit

is cleared by the debug engine once set . CPU writes to the TXC bit results in clearing of the PSS[1:0]

bits .