10 accumulator n register (a[n], 9h[nh]), 11 prefix register (pfx[n], bh[n]), 12 instruction pointer register (ip, ch[0h]) – Maxim Integrated MAX31782 User Manual

Page 27: 10accumulatornregister(a[n],9h[nh]), 11prefixregister(pfx[n],bh[n]), 12instructionpointerregister(ip,ch[0h])

MaximIntegrated 3-9

MAX31782 User’s Guide

Revision 0; 8/11

3.1.10AccumulatornRegister(A[n],9h[nh])

Initialization: This register is cleared to 0000h on all forms of reset .

Access: Unrestricted direct read/write access .

3.1.11PrefixRegister(PFX[n],Bh[n])

Initialization: This register is cleared to 0000h on all forms of reset .

Access: Unrestricted direct read/write access .

3.1.12InstructionPointerRegister(IP,Ch[0h])

Initialization: This register is cleared to 8000h on all forms of reset .

Access: Unrestricted direct read/write access .

BIT

FUNCTION

A[n] .[15:0]

This register acts as the accumulator for all ALU arithmetic and logical operations when selected by the

accumulator pointer (AP) . It can also be used as a general-purpose working register .

BIT

FUNCTION

PFX[n] .[15:0]

The Prefix register provides a means of supplying an additional 8 bits of high-order data for use by the

succeeding instruction as well as providing additional indexing capabilities . This register only holds any

data written to it for one execution cycle, after which it reverts to 0000h . Although this is a 16-bit register,

only the lower 8 bits are actually used for prefixing purposes by the next instruction . Writing to or reading

from any index in the prefix module selects the same 16-bit register . However, when the PFX register is

written, the index n used for the PFX[n] write also determines the high-order bits for the register source

and destination specified in the following instruction .

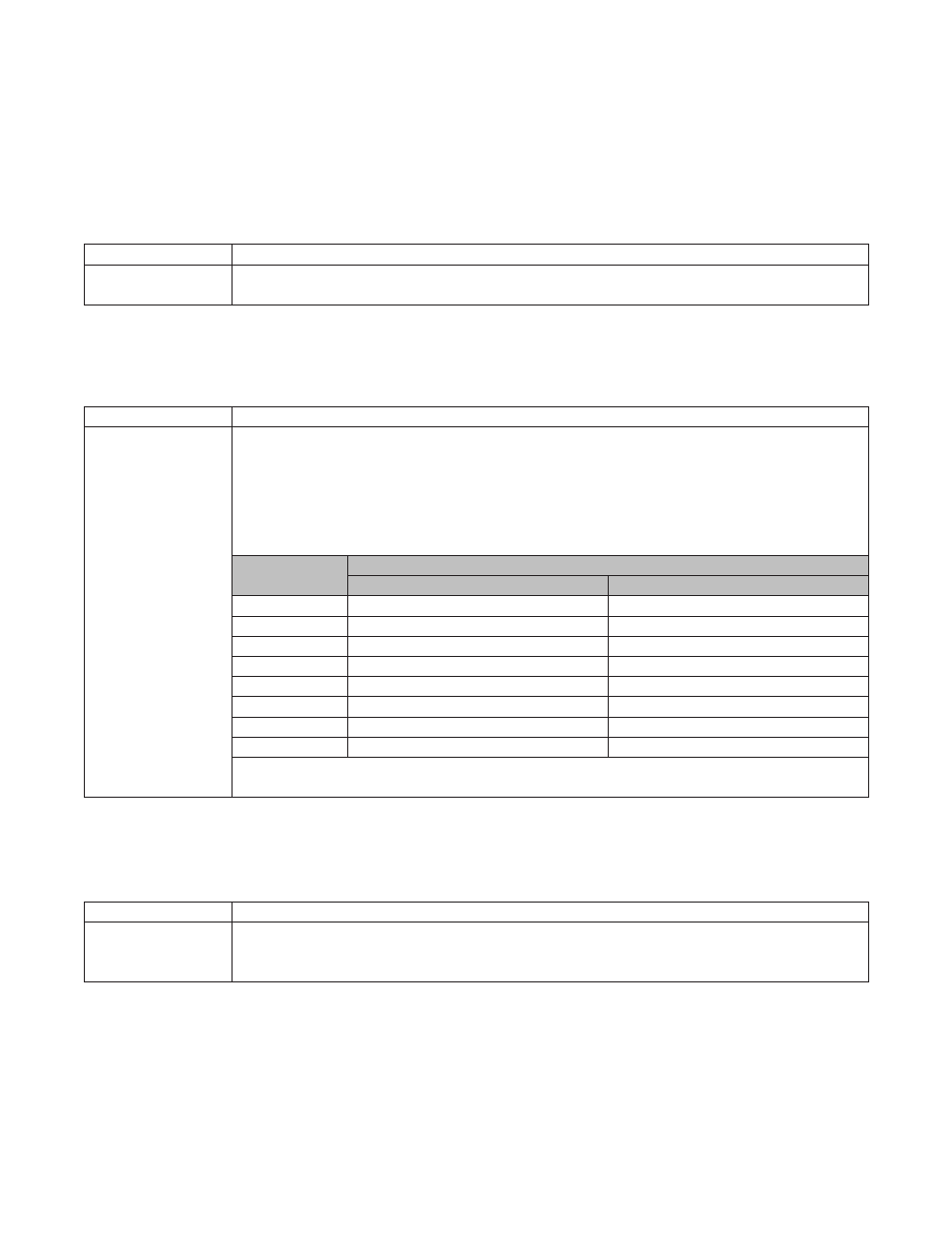

WRITE TO

SOURCE, DESTINATION INDEX SELECTION

SOURCE REGISTER RANGE

DESTINATION REGISTER RANGE

PFX[0]

0h to Fh

0h to 7h

PFX[1]

10h to 1Fh

0h to 7h

PFX[2]

0h to Fh

8h to Fh

PFX[3]

10h to 1Fh

8h to Fh

PFX[4]

0h to Fh

10h to 17h

PFX[5]

10h to 1Fh

10h to 17h

PFX[6]

0h to Fh

18h to 1Fh

PFX[7]

10h to 1Fh

18h to 1Fh

The index selection reverts to 0 (default mode allowing selection of registers 0h to 7h for destinations)

after one cycle in the same manner as the contents of the PFX register .

BIT

FUNCTION

IP .[15:0]

This register contains the address of the next instruction to be executed and is automatically incremented

by 1 after each program fetch . Writing an address value to this register caused program flow to jump to

that address . Reading from this register does not affect program flow .