1 multiplier control register (mcnt), 14 .5 .1 multiplier control register (mcnt) -6, 1multipliercontrolregister(mcnt) – Maxim Integrated MAX31782 User Manual

Page 121

MaximIntegrated 14-6

MAX31782 User’s Guide

Revision 0; 8/11

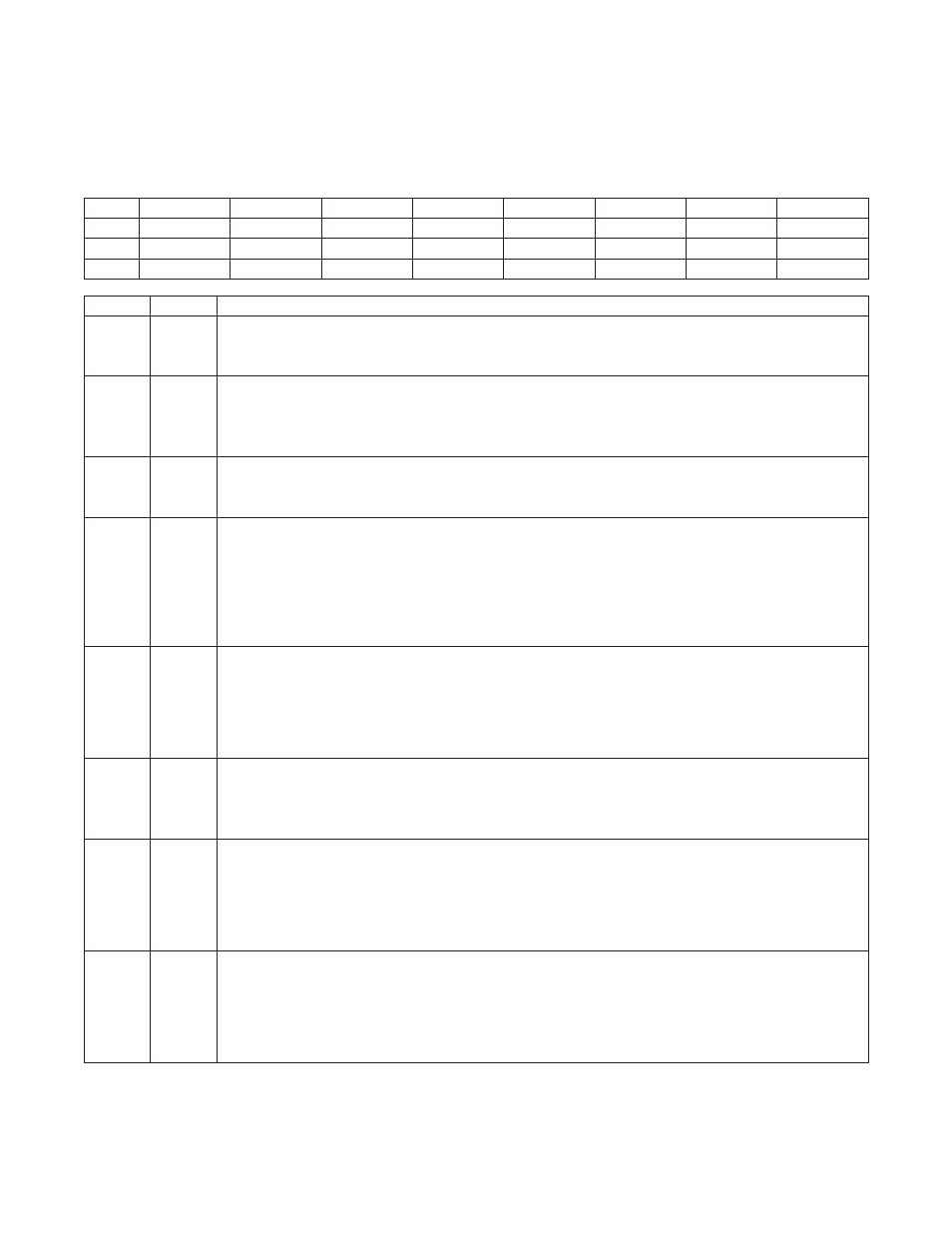

14.5.1MultiplierControlRegister(MCNT)

Bit

7

6

5

4

3

2

1

0

Name

OF

MCW

CLD

SQU

OPCS

MSUB

MMAC

SUS

Reset

0

0

0

0

0

0

0

0

Access

r

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

7

OF

OverflowFlag . This bit is set to logic 1 when an overflow occurred for the last operation . This bit can be

set for accumulation/subtraction operations or unsigned multiply-negate attempts . This bit is automatically

cleared to 0 following a reset, starting a multiplier operation, or setting of the CLD bit to 0 .

6

MCW

MCRegisterWriteSelect . The state of the MCW bit determines if an operation result will be placed into

the accumulator registers (MC) .

0 = The result will be written to the MC registers .

1 = The result is not written to the MC registers (MC register content is unchanged) .

5

CLD

ClearDataregister . This bit initializes the operand registers and the accumulator of the multiplier . When it

is set to 1, the contents of all data registers and the OF bit are cleared to 0 and the operand load counter

is reset immediately . This bit is cleared by hardware automatically . Writing a 0 to this bit has no effect .

4

SQU

SquareFunctionEnable . This bit supports the hardware square function . When this bit is set to logic 1, a

square operation is initiated after an operand is written to either the MA or the MB register . Writing data to

either of the operand registers writes to both registers and triggers the specified square or square-accu-

mulate/subtract operation . Setting this bit to 1 also overrides the OPCS bit setting . When SQU is cleared to

logic 0, the hardware square function is disabled .

0 = Square function disabled

1 = Square function enabled

3

OPCS

OperandCountSelect . This bit defines how many operands must be loaded to trigger a multiply or multi-

ply-accumulate/subtract operation (except when SQU = 1, since this implicitly specifies a single operand) .

When this bit is cleared to logic 0, both operands (MA and MB) must be written to trigger the operation .

When this bit is set to 1, the specified operation is triggered once either operand is written .

0 = Both operands (MA and MB) must be written to trigger the multiplier operation .

1 = Loading one operand (MA or MB) triggers the multiplier operation .

2

MSUB

Multiply-AccumulateNegate . Configuring this bit to logic 1 enables negation of the product for signed

multiply operations and subtraction of the product from the accumulator (MC[2:0]) when MMAC = 1 . When

MSUB is configured to logic 0, the product of multiply operations will not be negated and accumulation is

selected when MMAC = 1 .

1

MMAC

Multiply-AccumulateEnable . This bit enables the accumulate or subtract operation (as per MSUB) for

the hardware multiplier . When this bit is cleared to logic 0, the multiplier performs only multiply operations .

When this bit is set to logic 1, the multiplier performs a multiply-accumulate or multiply-subtract operation

based upon the MSUB bit .

0 = Accumulate/subtract operation disabled

1 = Accumulate/subtract operation enabled

0

SUS

Signed-Unsigned . This bit determines the data type of the operands . When this bit is cleared to logic

0, the operands are treated as two’s complement values and the multiplier performs a signed operation .

When this bit is set to logic 1, the operands are treated as absolute magnitudes and the multiplier per-

forms an unsigned operation .

0 = Signed operands

1 = Unsigned operands