2 multiplier operand a register (ma), 3 multiplier operand b register (mb), 4 multiplier accumulator 2 register (mc2) – Maxim Integrated MAX31782 User Manual

Page 122: 5 multiplier accumulator 1 register (mc1), 6 multiplier accumulator 0 register (mc0), 2multiplieroperandaregister(ma), 3multiplieroperandbregister(mb), 4multiplieraccumulator2register(mc2), 5multiplieraccumulator1register(mc1), 6multiplieraccumulator0register(mc0)

MaximIntegrated 14-7

MAX31782 User’s Guide

Revision 0; 8/11

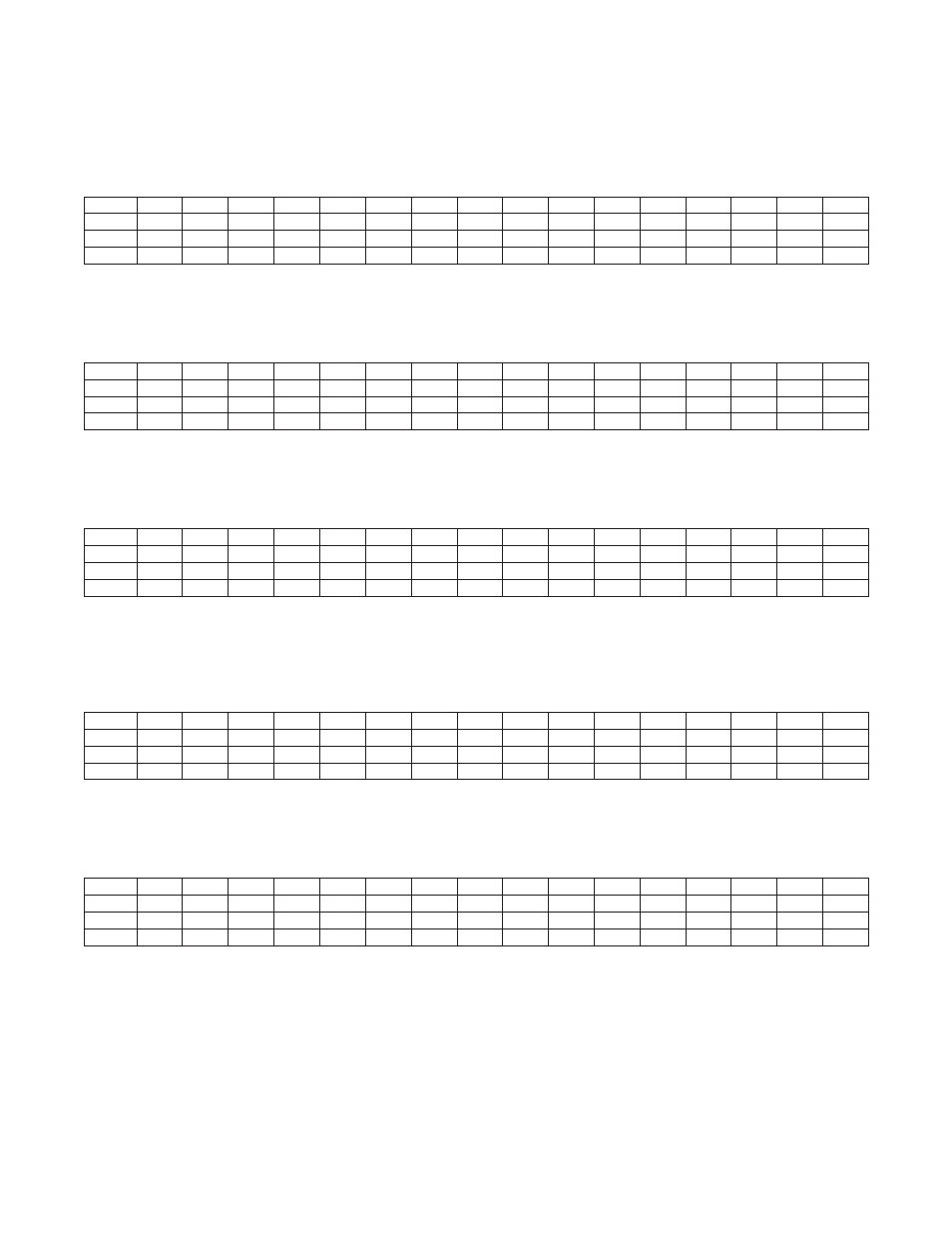

14.5.2MultiplierOperandARegister(MA)

MultiplierOperandARegister.This operand A register is used by the application code to load 16-bit values for mul-

tiplier operations .

14.5.3MultiplierOperandBRegister(MB)

MultiplierOperandBRegister.This operand B register is used by the application code to load 16-bit values for mul-

tiplier operations .

14.5.4MultiplierAccumulator2Register(MC2)

MultiplierAccumulator2Register.The MC2 register represents the two most significant bytes of the accumulator

register . The 48-bit accumulator is formed by MC2, MC1, and MC0 . For a signed operation, the most significant bit of

this register is the sign bit .

14.5.5MultiplierAccumulator1Register(MC1)

MultiplierAccumulator1Register: The MC1 register represents bytes 3 and 2 of the accumulator register . The 48-bit

accumulator is formed by MC2, MC1, and MC0 .

14.5.6MultiplierAccumulator0Register(MC0)

MultiplierAccumulator0Register:The MC0 register represents the two least significant bytes of the accumulator

register . The 48-bit accumulator is formed by MC2, MC1, and MC0 .

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

MA .15

MA .14

MA .13

MA .12

MA .11

MA .10

MA .9

MA .8

MA .7

MA .6

MA .5

MA .4

MA .3

MA .2

MA .1

MA .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

MB .15

MB .14

MB .13

MB .12

MB .11

MB .10

MB .9

MB .8

MB .7

MB .6

MB .5

MB .4

MB .3

MB .2

MB .1

MB .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

MC2 .15

MC2 .14

MC2 .13

MC2 .12

MC2 .11

MC2 .10

MC2 .9

MC2 .8

MC2 .7

MC2 .6

MC2 .5

MC2 .4

MC2 .3

MC2 .2

MC2 .1

MC2 .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

MC1 .15

MC1 .14

MC1 .13

MC1 .12

MC1 .11

MC1 .10

MC1 .9

MC1 .8

MC1 .7

MC1 .6

MC1 .5

MC1 .4

MC1 .3

MC1 .2

MC1 .1

MC1 .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

MC0 .15

MC0 .14

MC0 .13

MC0 .12

MC0 .11

MC0 .10

MC0 .9

MC0 .8

MC0 .7

MC0 .6

MC0 .5

MC0 .4

MC0 .3

MC0 .2

MC0 .1

MC0 .0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw

rw