2 adc register descriptions, 1 adc control register (adcn), 6 .2 adc register descriptions -6 – Maxim Integrated MAX31782 User Manual

Page 49: 6 .2 .1 adc control register (adcn) -6, 2adcregisterdescriptions, 1adccontrolregister(adcn)

MaximIntegrated 6-6

MAX31782 User’s Guide

Revision 0; 8/11

6.2ADCRegisterDescriptions

The ADC is controlled by ADC SFR registers . Four of the registers, ADST, ADADDR, ADCN, and ADDATA, are used for

setup, control, and reading from the ADC . There are five other registers, ETS, ADCG1, ADCG5, ADVOFF, and TOEX,

which are used to adjust the gains and offsets applied to ADC results . To avoid undesired operations, the user should

not write to bits labeled as reserved .

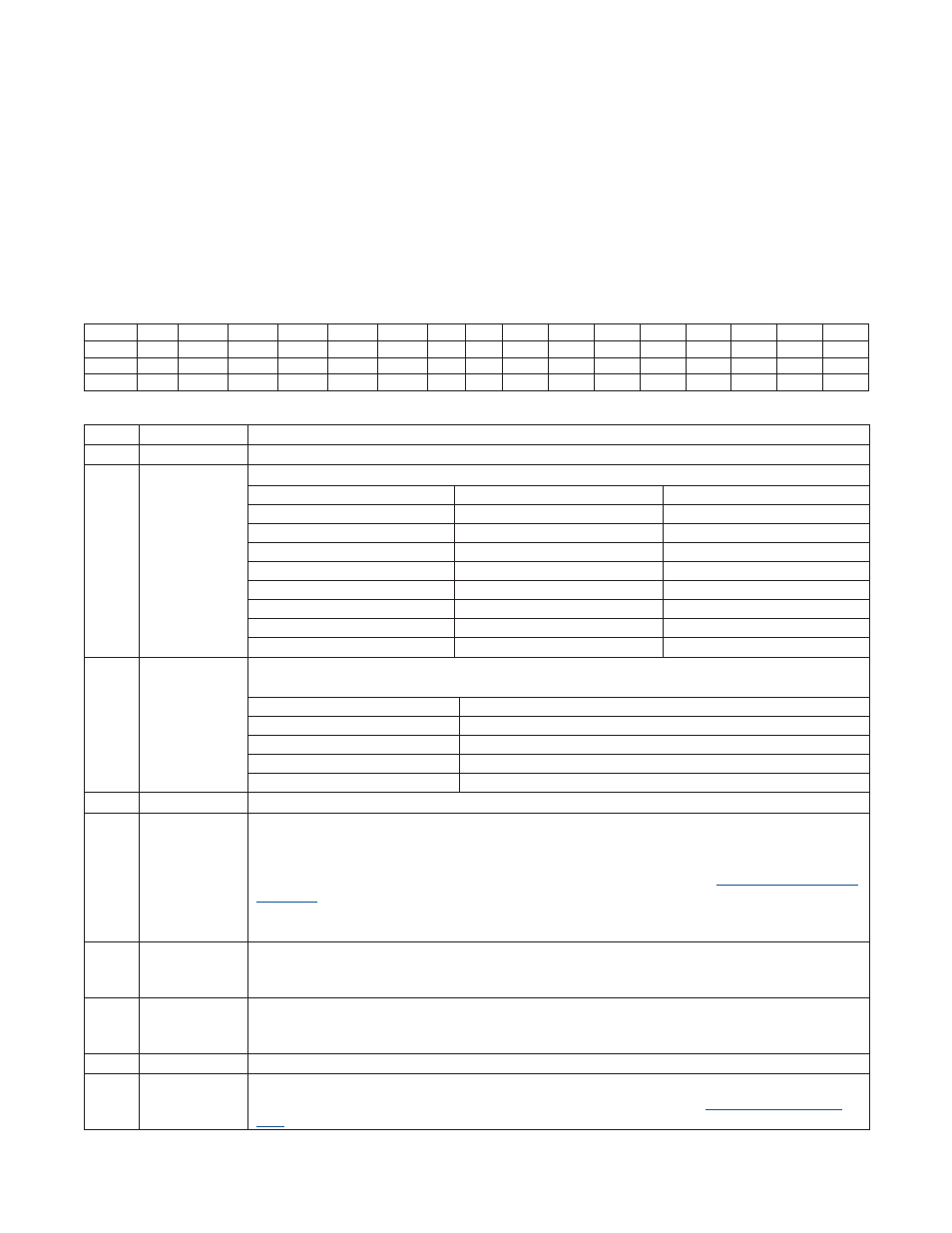

6.2.1ADCControlRegister(ADCN)

Register Address: M2[08h]

*Unrestricted read, but can only be written to when ADCONV = 0.

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

—

ADCCLK2 ADCCLK1 ADCCLK0 ADDAINV1 ADDAINV0

—

—

IREFEN ADCONT ADDAIE

—

ADACQ3 ADACQ2 ADACQ1 ADACQ0

Reset

0

0

1

1

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

rw*

rw*

rw*

rw*

rw*

r

r

rw*

rw*

rw*

r

rw*

rw*

rw*

rw*

BIT

NAME

DESCRIPTION

15

—

Reserved . The user should not write to this bit .

14:12

ADCCLK[2:0]

ADC Clock Divider . These bits select the ADC conversion clock in relationship to the system clock .

ADCCLK[2:0]

READAS

ADCCLOCK

000

011

Sysclk/16

001

011

Sysclk/16

010

011

Sysclk/16

011

011

Sysclk/16

100

100

Sysclk/16

101

101

Sysclk/32

110

110

Sysclk/64

111

111

Sysclk/128

11:10

ADDAINV[1:0]

ADC Data Available Interrupt Interval . These bits select the condition for setting data available inter-

rupt flag (ADDAI) .

ADDAINV[1:0]

SETADDAIAT

00

Every ADC sample

01

End of every sequence (ADSTART to ADEND)

10

Every 12 ADC samples

11

Every 16 ADC samples

9:8

—

Reserved . The user should not write to these bits .

7

IREFEN

Internal Reference Enable . For voltage mode inputs, setting this bit to 1 enables the internal refer-

ence and clearing this bit to 0 chooses external reference sourced from pin AD3N . If the channel

select bits equal 6 or 7 or if the external temperature mode is chosen, then the internal reference is

chosen regardless of IREFEN setting . If an external reference is desired, see

for more information . When the internal reference is used, the FS can be set to factory pro-

grammed settings, 1 .225V or 5 .5V . The appropriate FS is chosen by the ADGAIN bit described in the

configuration section .

6

ADCONT

ADC Continuous Sequence Mode . Setting this bit to 1 enables the continuous sequence mode .

Clearing this bit to 0 disables the continuous sequence mode . In single sequence mode, the ADC

conversion stops after the end of the sequence .

5

ADDAIE

ADC Data Available Interrupt Enable . Setting the ADDAIE bit to 1 enable an interrupt to be generated

to the CPU when the ADDAI = 1 . Clearing this bit to 0 disables an interrupt from generating when

ADDAI = 1 .

4

—

Reserved . The user should not write to this bit .

3:0

ADACQ[3:0]

ADC Acquisition Extension Bits [3:0] . These bits are used to extend sample acquisition time if the

corresponding ADC acquisition extension is enabled (ADACQEN = 1) . See

for details .