Maxim Integrated MAX31782 User Manual

Page 41

MaximIntegrated 5-6

MAX31782 User’s Guide

Revision 0; 8/11

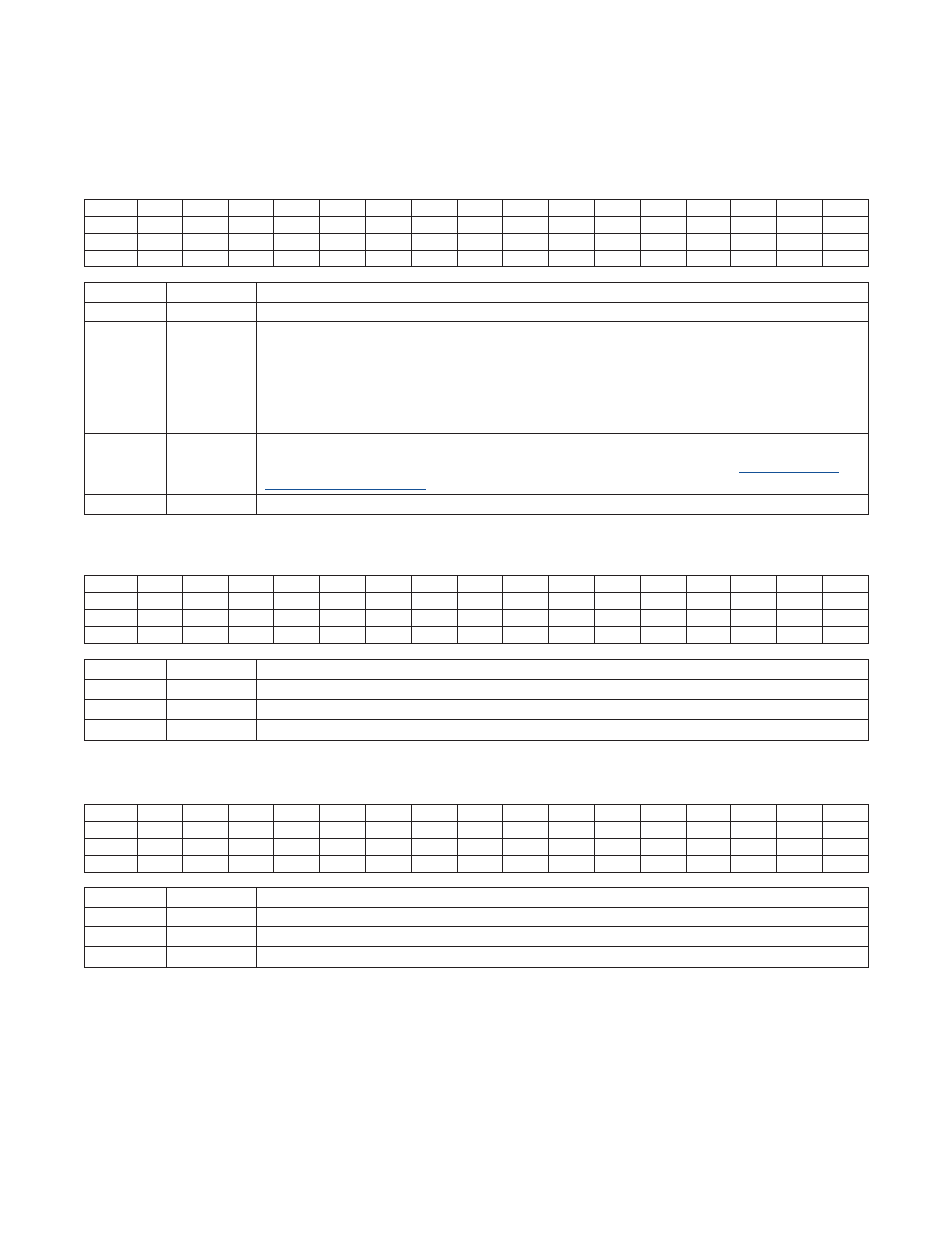

5.2.3PeripheralModule2InterruptIdentificationRegister(MIIR2,M2[03h])

5.2.4PeripheralModule3InterruptIdentificationRegister(MIIR3,M3[10h])

5.2.5PeripheralModule4InterruptIdentificationRegister(MIIR4,M4[10h])

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

—

—

—

—

—

—

—

—

I2CS_WU

I2CS

ADC

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:3

—

Reserved . A read returns 0 .

2

I2CS_WU

This bit is set when there is a wake-up interrupt from the I

2

C slave block . A wake-up interrupt is

defined as an I

2

C START signal only when the CPU is operating in stop mode . As the CPU clock

is not running in stop mode, this is an asynchronous interrupt . This interrupt causes the MAX31782

to automatically transition from stop mode to CPU mode . The wake-up interrupt shares the same

enable bits as the slave I

2

C START interrupt I2CSRI . Once set, this bit is cleared by clearing the

I2CST_S .I2CSRI bit .

1

I2CS

This bit is set when there is an interrupt from the I

2

C slave block . The I

2

C interrupt is a combina-

tion of all interrupts defined in the I2CST_S register for the I

2

C slave block . See

for more details on the individual interrupts .

0

ADC

This bit is set when there is an interrupt from the ADC .

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

—

—

—

—

—

—

—

—

—

TACH1

TACH0

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:2

—

Reserved . A read returns 0 .

1

TACH1

This bit is set when there is an interrupt from tachometer 1 (TACH .1) .

0

TACH0

This bit is set when there is an interrupt from tachometer 0 (TACH .0) .

Bit

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Name

—

—

—

—

—

—

—

—

—

—

—

—

—

—

TACH3

TACH2

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

r

BIT

NAME

DESCRIPTION

15:2

—

Reserved . A read returns 0 .

1

TACH3

This bit is set when there is an interrupt from tachometer 3 (TACH .3) .

0

TACH2

This bit is set when there is an interrupt from tachometer 2 (TACH .2) .