7 interrupt identification register (iir, 8h[bh]), 8 system clock control register (ckcn, 8h[eh]), 7interruptidentificationregister(iir,8h[bh]) – Maxim Integrated MAX31782 User Manual

Page 25: 8systemclockcontrolregister(ckcn,8h[eh])

MaximIntegrated 3-7

MAX31782 User’s Guide

Revision 0; 8/11

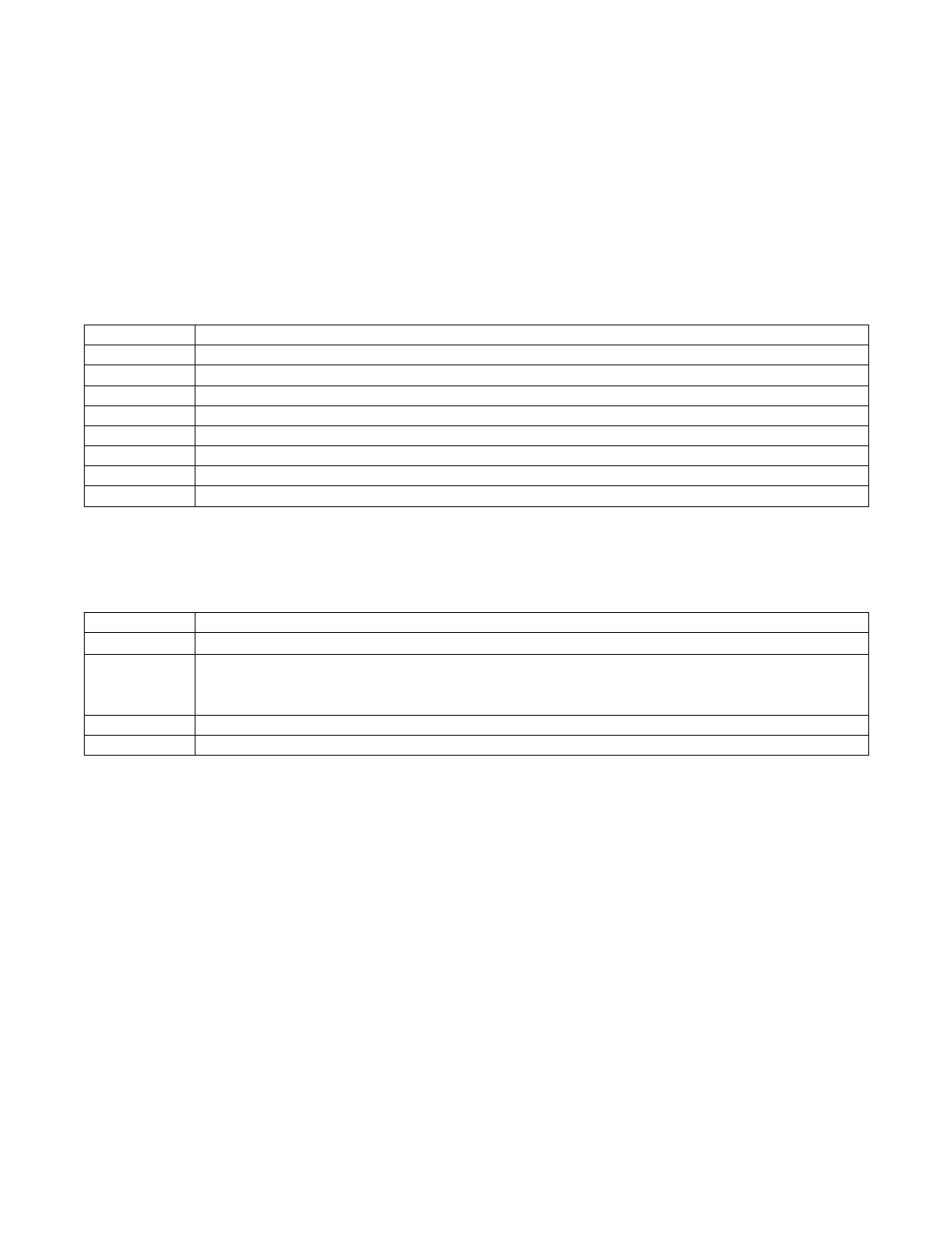

3.1.7InterruptIdentificationRegister(IIR,8h[Bh])

Initialization: This register is cleared to 00h on all forms of reset .

Access: Read-only .

3.1.8SystemClockControlRegister(CKCN,8h[Eh])

Initialization: This register is cleared to 10h on all forms of reset .

Access: Unrestricted read/write access .

The first six bits in this register indicate interrupts pending in modules 0 to 5, one bit per module . The eighth bit, IIS, indicates a

pending system interrupt, such as from the watchdog timer . The interrupt pending flags are set only for enabled interrupt sources

waiting for service . The interrupt pending flag is cleared when the pending interrupt sources within that module are disabled or

when the interrupt flags are cleared by software .

BIT

FUNCTION

IIR .0 (II0)

Interrupt Identifier Flag for Register Module 0

IIR .1 (II1)

Interrupt Identifier Flag for Register Module 1

IIR .2 (II2)

Interrupt Identifier Flag for Register Module 2

IIR .3 (II3)

Interrupt Identifier Flag for Register Module 3

IIR .4 (II4)

Interrupt Identifier Flag for Register Module 4

IIR .5 (II5)

Interrupt Identifier Flag for Register Module 5

IIR .6

Reserved . Reads return 0 .

IIR .7 (IIS)

Interrupt Identifier Flag for System Modules

BIT

FUNCTION

CKCN .[3:0]

Reserved . All reads return 0 .

CKCN .4 (STOP)

Stop Mode Select . Setting this bit to 1 stops program execution and commences low-power operation . This

bit is cleared by a reset or any of the enabled external interrupts . Setting and resetting the STOP bit does not

change the system clock source and its divide ratio .

CKCN .[6:5]

Reserved . All reads return 0 .

CKCN .7

Reserved . All reads return 1 .