2 watchdog timer reset, 3 external reset, 4 internal system resets – Maxim Integrated MAX31782 User Manual

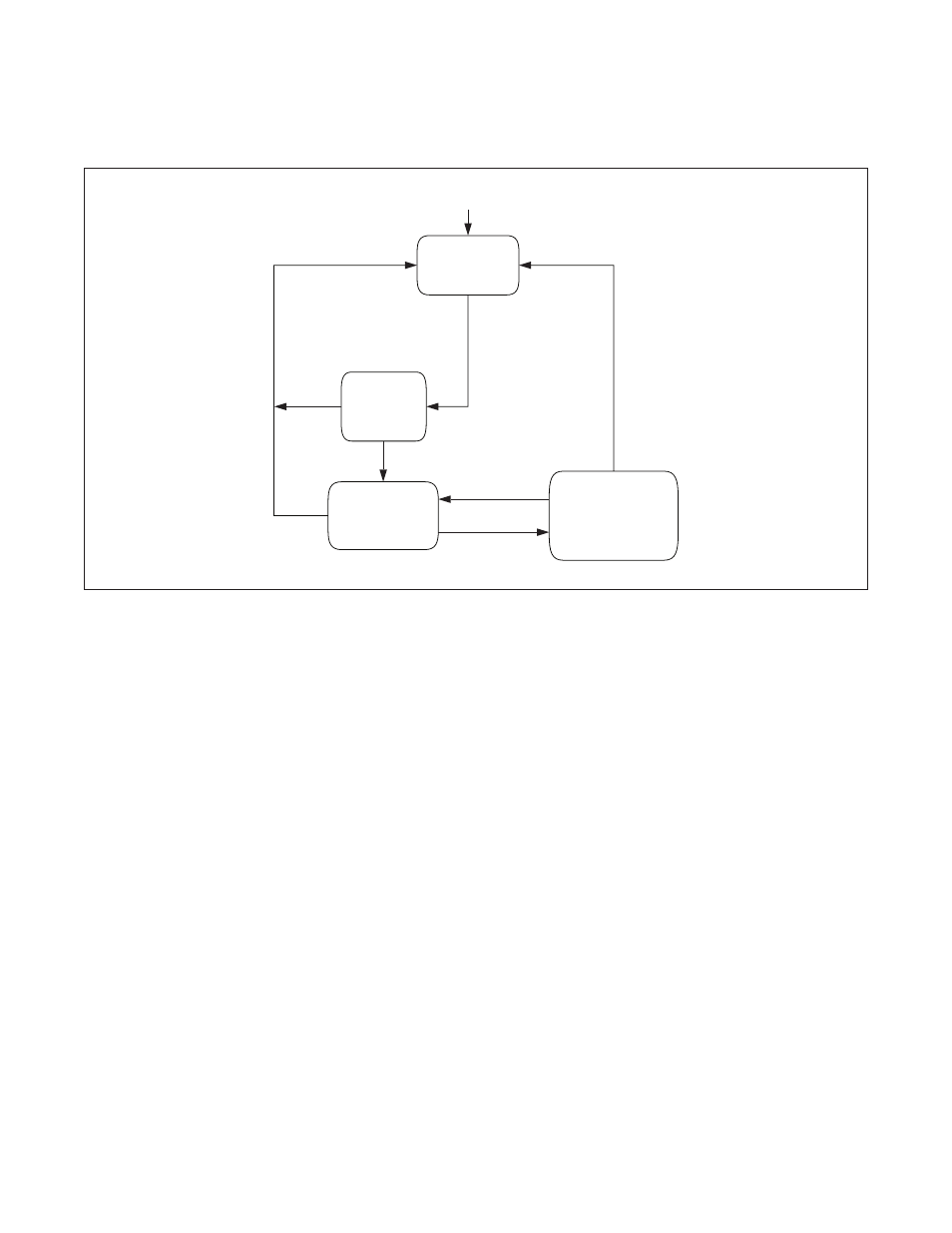

Page 17: Figure 2-6 . max31782 state diagram -13, 2watchdogtimerreset, 3externalreset, 4internalsystemresets

MaximIntegrated 2-13

MAX31782 User’s Guide

Revision 0; 8/11

2.6.2WatchdogTimerReset

The watchdog timer is a programmable hardware timer that can be used to reset the processor in case a software

lockup or other unrecoverable error occurs . Once the watchdog is enabled, software must reset the watchdog timer

periodically . If the processor does not reset the watchdog timer before it elapses, the watchdog can initiate a reset .

If the watchdog resets the processor, the MAX31782 remains in reset and holds the RST pin low for 12 clock cycles .

When a reset occurs due to a watchdog timeout, the watchdog timer reset flag (WTRF) in the WDCN register is set to

indicate the source of the reset .

2.6.3ExternalReset

During normal operation, the MAX31782 is placed into external reset when the RST pin is held at logic 0 for at least four

clock cycles . Once the MAX31782 enters reset mode, it remains in reset as long as the RST pin is held at logic 0 . After

the RST pin returns to logic 1, the processor exits reset within 12 clock cycles .

An external reset pulse on the RST pin can also bring the MAX31782 out of its low-power stop mode . When this occurs,

the MAX31782 resets and returns to normal CPU mode operation within 10 clock cycles .

2.6.4InternalSystemResets

There are two possible sources of internal system resets . An internal reset holds the MAX31782 in reset mode for 12

clock cycles .

1) When data BBh is written to the special I

2

C slave address 34h .

2) When in-system programming is complete and the ROD bit is set to 1 .

Figure 2-6. MAX31782 State Diagram

POR

SYSTEM CLOCK

STARTUP DELAY

t

SU:MOSC

PORT6 GPIO INT, I

2

C

START INT, SVM INT

OR EXT RESET

CKCN.STOP = 1

V

DD

> V

BO

V

DD

< V

BO

V

DD

< V

BO

V

DD

< V

BO

BROWNOUT STATE

CPU DISABLED

ANALOG ACTIVE

CPU MODE

DIGITAL CORE ON

ANALOG ON

CODE IS EXECUTING

STOP MODE

DIGITAL CORE OFF

ANALOG ON

SVM MONITOR DEPENDS

ON SVMEN AND SVMSTOP