1 background mode operation, 17 .1 background mode operation -3, Figure 17-2 . 10-bit word format -3 – Maxim Integrated MAX31782 User Manual

Page 138: Figure 17-2, Table 17-1, 1backgroundmodeoperation

MaximIntegrated 17-3

MAX31782 User’s Guide

Revision 0; 8/11

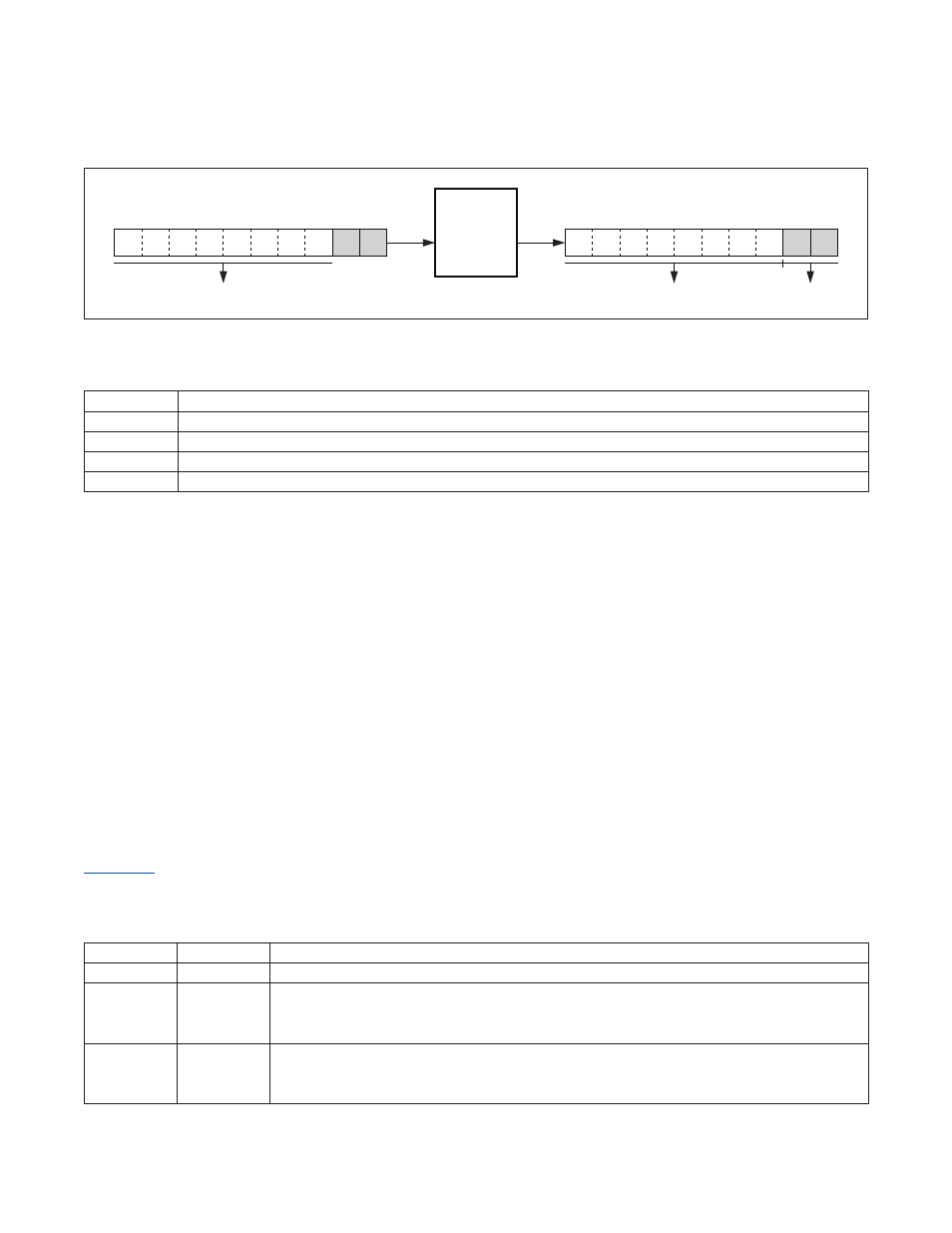

The data byte portion of the 10-bit shift register is interfaced directly to the ICDB parallel register . The ICDB register

functions as the holding data register for both transmit and receive operations . On the falling edge of TCK in the Update-

DR state, the outgoing data is loaded from the ICDB parallel register to the debug shift register and the incoming shift

register data is latched in the ICDB parallel register .

17.1BackgroundModeOperation

When the instruction register is loaded with the Debug instruction (IR[2:0] = 010b), the host can communicate with the

MAX31782 in a background mode using TAP DR-Scan sequences without disturbing CPU operation . Note, however,

that JTAG in-system programming also requires use of the 10-bit debug shift register and, if enabled (JTAG_SPE = 1,

PSS[1:0] = 0), takes precedence over background mode communication . When operating in background mode, the

status bits are always cleared to 00b (non-debug), which indicates that the MAX31782 is ready to receive background

mode commands .

The host can perform the following operations from background mode:

• read/write internal breakpoint registers (BP0–BP5)

• read/write internal in-circuit debug registers (ICDC, ICDF, ICDA, ICDD)

• monitor to determine when a breakpoint match has occurred

• directly invoke debug mode

shows the background mode commands supported by the MAX31782 . Encodings not listed in this table are

not supported in background mode and are treated as no operations .

Figure 17-2. 10-Bit Word Format

Table17-1.StatusBits

Table17-2.BackgroundModeCommands

s[1:0]

STATUS/CONDITION

00

Non-Debug. Default condition, background mode, or debug engine inactive .

01

DebugIdle. Debug engine is ready to receive data from the host (command, data) .

10

DebugBusy. Debug engine is busy without valid data (i .e ., ROM code execution, trace operations) .

11

DebugValid. Debug engine is busy with valid data .

OPCODE

COMMAND

OPERATION

0000–0000

No Operation Nooperation. Default state for debug shift register .

0000–0001

Read ICDC

ReadcontroldatafromtheICDC. The contents of the ICDC register is loaded into the debug

shift register through the ICDB register for host read . This command requires one follow-on trans-

fer cycle .

0000–0010

Read ICDF

ReadflagsfromtheICDF. The contents of the ICDF register (1 byte) are loaded into the debug

shift register through the ICDB register for host read . This command requires one follow-on trans-

fer cycle .

TDI

TDO

9

0

9

0

X

X

s0

s1

HOST COMMAND/DATA INPUT

MAX31782 DATA OUTPUT

STATUS

MAX31782