2 up/down count pwm output mode, 12 .1 .5 .2 up/down count pwm output mode -9, Figure 12-7 – Maxim Integrated MAX31782 User Manual

Page 111: 2up/downcountpwmoutputmode

MaximIntegrated 12-9

MAX31782 User’s Guide

Revision 0; 8/11

12.1.5.2Up/DownCountPWMOutputMode

The Timer B can also operate in an up/down count configuration when in PWM output mode by setting DCEN = 1 . The

timer counts upward until it reaches the value in the reload register (TB0R) . On the next cycle, it reverses the count

direction and starts counting down . When the TB0V counter reaches 0000h, it again reverses direction and begins

counting up .

When operating in an up/down count configuration and either set or reset mode, the PWM effectively allows 17-bit

resolution . In set mode the duty cycle is always less than 50%, and in reset mode the duty cycle is always greater than

50% . The toggle mode provides a center-aligned 16-bit PWM with twice the period of the up counting PWM output

mode .

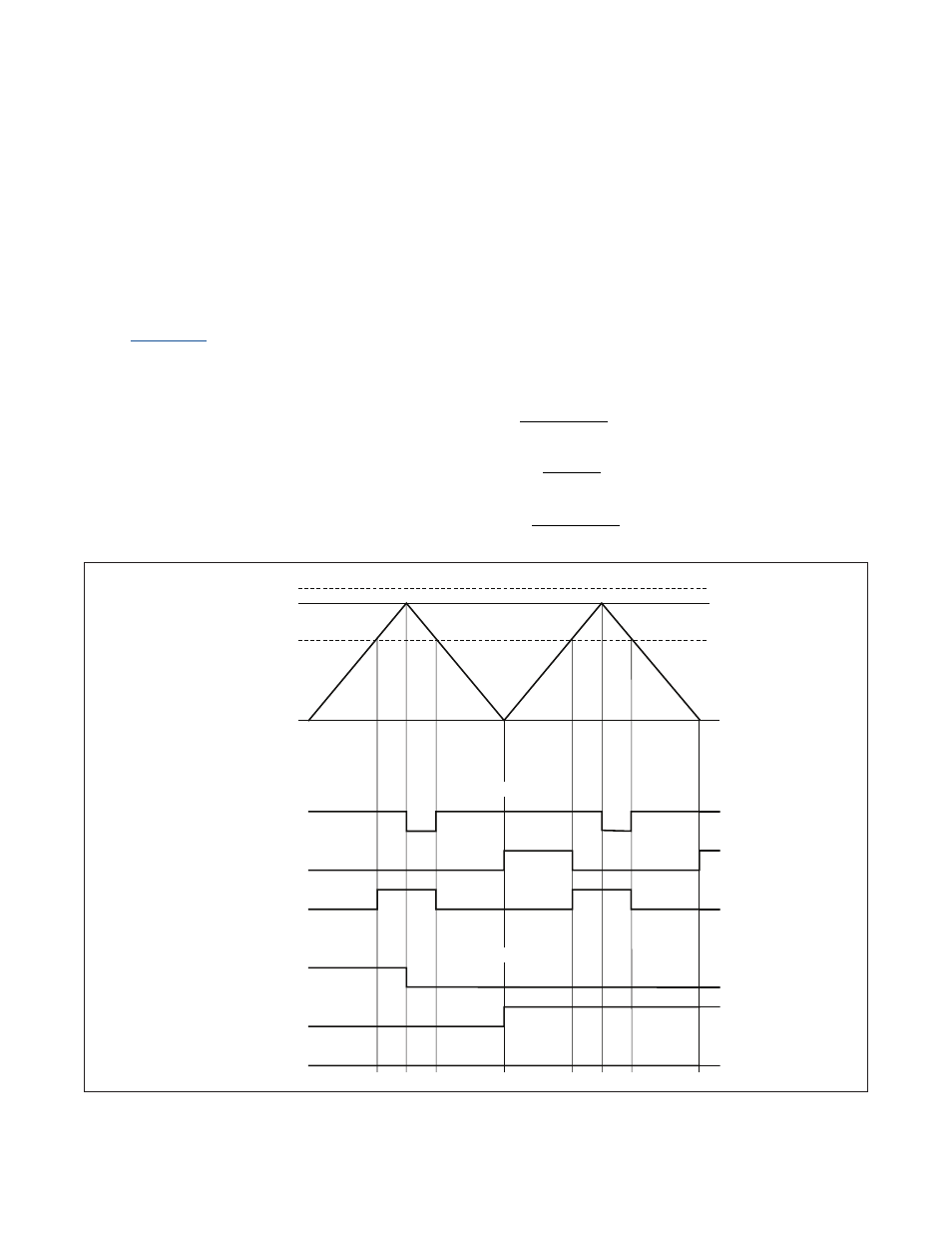

illustrates the PWM waveforms when the Timer B is operating in up/down count PWM output mode .

The up/down count PWM output period and duty cycle are calculated as follows:

PERIOD = 2

× TB0R × TIMER B CLOCK PERIOD

Duty Cycle in Set Mode =

TB0R TB0C

2 TB0R

+

×

Duty Cycle in Reset Mode =

TB0C

2 TB0R

×

Duty Cycle in Toggle Mode =

TB0R TB0C

TB0R

−

Figure 12-7. TBB Pin Waveform in Up/Down Count PWM Output Mode

TB0C > TB0R

TB0C < TB0R

0000h

TB0V

SET MODE

RESET MODE

TOGGLE MODE

SET MODE

RESET MODE

TOGGLE MODE

TB0R

TB0C < TB0R

TB0C > TB0R