Table 17-3 . debug mode commands -9, Table17-3.debugmodecommands – Maxim Integrated MAX31782 User Manual

Page 144

MaximIntegrated 17-9

MAX31782 User’s Guide

Revision 0; 8/11

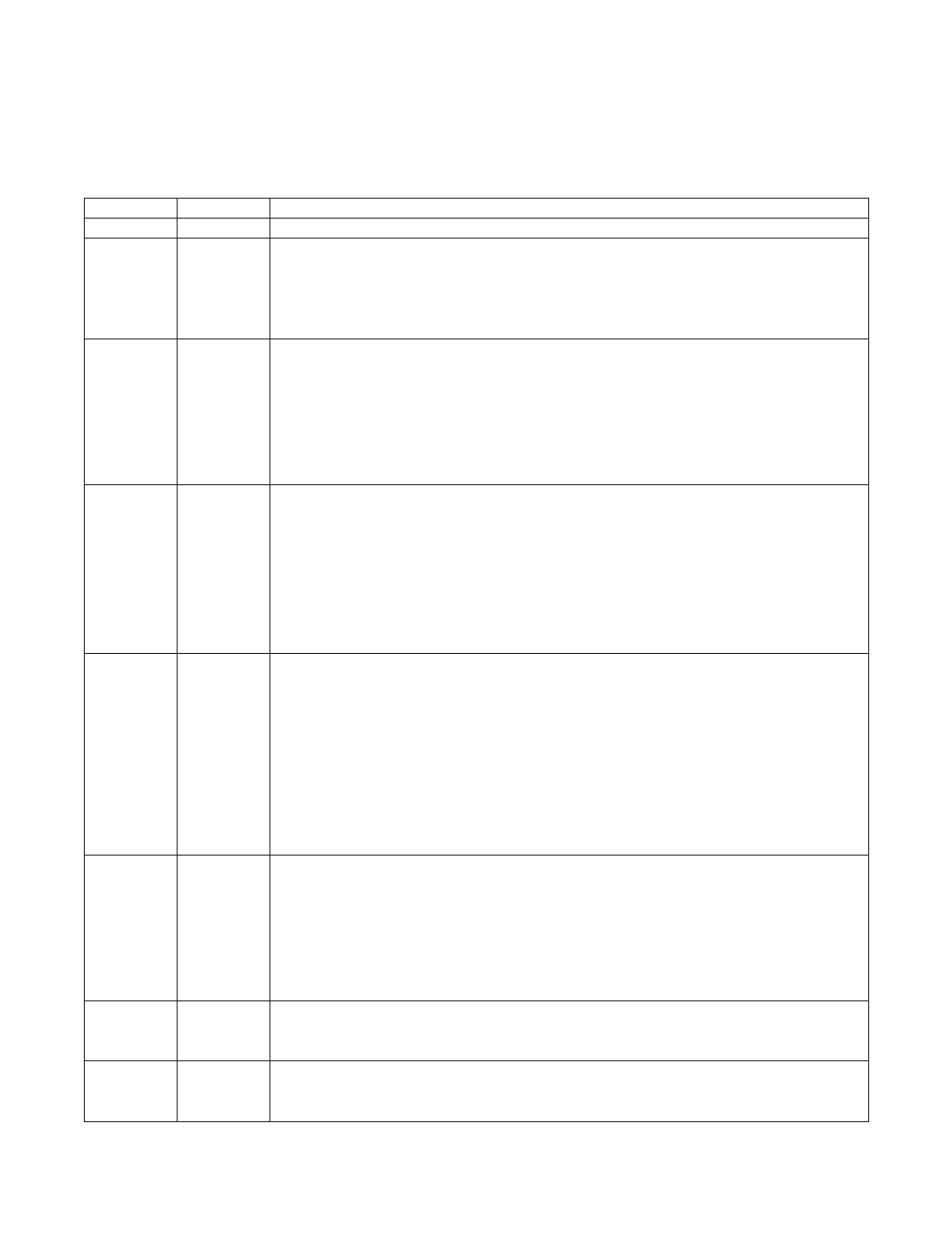

Table17-3.DebugModeCommands

OPCODE

COMMAND

OPERATION

0010–0000

No Operation Nooperation.

0010–0001

Read register

Map

Readdatafrominternalregisters.This command forces the debug engine to update the

CMD[3:0] bits in the ICDC to 0001b and perform a jump to ROM code at x8010h . The ROM debug

service routine loads register data to ICDB for host capture/read, starting at the lowest register

location in module 0, one byte at a time in a successive order until all internal registers are read

and output to the host .

0010–0010

Read data

memory

Readdatafromdatamemory. This command requires four follow-on transfer cycles, two for the

starting address and two for the word read count, starting with the LSB address and ending with

the MSB read count . The input address must be based memory map when executing from utility

ROM, as shown in Figure 2-4 . The address is moved to the ICDA register and the word read count

is moved to the ICDD register by the debug engine . This information is directly accessible by the

ROM code . At the completion of this command period, the debug engine updates the CMD[3:0]

bits to 0010b and performs a jump to ROM code at x8010h . The ROM debug service routine loads

ICDB from data memory according to address and count information provided by the host .

0010–0011

Read pro-

gram stack

Readdatafromprogramstack. This command requires four follow-on transfer cycles, two for

the starting address and two for the read count, starting with the LSB address and ending with

the MSB read count . The address is moved to the ICDA register and the read count is moved to

the ICDD register by the debug engine . This information is directly accessible by the ROM code .

At the completion of this command period, the debug engine updates the CMD[3:0] bits to 0011b

and performs a jump to ROM code at x8010h . The ROM debug service routine pops data out from

the stack according to the information received in the ICDA and ICDD register .

The address input

is the highest value that is used, as words are popped off the stack and returned in descending

order .

0010–0100

Write register

Writedatatoaselectedregister. This command requires four follow-on transfer cycles, two for

the register address and two for the data, starting with the LSB address and ending with the MSB

data . The address is moved to the ICDA register and the data is moved to the ICDD register by

the debug engine . This information is directly accessible by the ROM code . At the completion of

this command period, the debug engine updates the CMD[3:0] bits to 0100b and performs a jump

to ROM code at x8010h . The ROM debug service routine updates the select register according

to the information received in the ICDA and ICDD registers .

Any register location can be written

using this command, including reserved locations and those used for op code support . No protec-

tion is provided by the debugging interface, and avoiding side effects is the responsibility of the

host system communicating with the MAX31782 . Writing to the IP register alters the address that

execution resumes from when the debugging engine exits .

0010–0101

Write data

memory

Writedatatoaselecteddatamemorylocation. This command requires four follow-on transfer

cycles, two for the memory address and two for the data, starting with the LSB address and ending

with the MSB data . The input address must be based memory map when executing from utility ROM,

as shown in Figure 2-4 . The address is moved to the ICDA register and the data is moved to the

ICDD register by the debug engine . This information is directly accessible by the ROM code . At the

completion of this command period, the debug engine updates the CMD[3:0] bits to 0101b and per-

forms a jump to ROM code at x8010h . The ROM debug service routine updates the selected data

memory location according to the information received in the ICDA and ICDD registers .

0010–0110

Trace

Tracecommand. This command allows single stepping the CPU and requires no follow-on trans-

fer cycle . The trace operation is a ‘debug mode exit, one cycle CPU execution, debug mode entry’

sequence .

0010–0111

Return

Returncommand. This command terminates the debug mode and returns the debug engine to

background mode . This allows the CPU to resume its normal operation at the point where it has

been last interrupted .