4 watchdog timer control register (wdcn), 15 .2 .4 watchdog timer control register (wdcn) -4, 4watchdogtimercontrolregister(wdcn) – Maxim Integrated MAX31782 User Manual

Page 128

MaximIntegrated 15-4

MAX31782 User’s Guide

Revision 0; 8/11

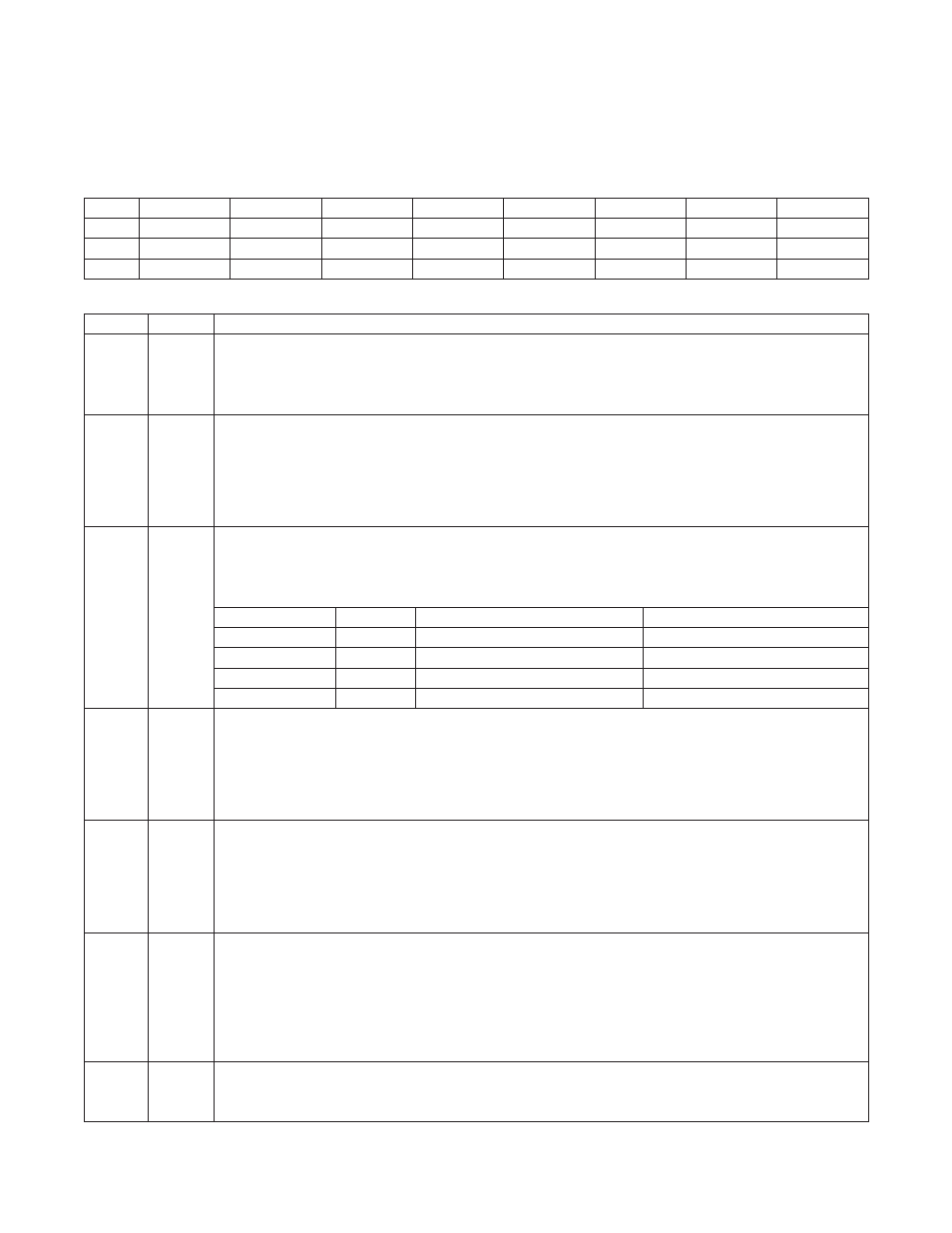

15.2.4WatchdogTimerControlRegister(WDCN)

*Bits 5, 4, 3 and 0 are cleared to 0 on all forms of reset; for others, see individual bit descriptions.

Bit

7

6

5

4

3

2

1

0

Name

POR

EWDI

WD1

WD0

WDIF

WTRF

EWT

RWT

Reset

s*

s*

0

0

0

s*

s*

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

BIT

NAME

DESCRIPTION

7

POR

Power-On-Reset Flag . This bit is set to 1 whenever a power-on/brownout reset occurs . It is unaffected by

other forms of reset . This bit can be checked by software following a reset to determine if a power-on/

brownout reset occurred . It should always be cleared by software following a reset to ensure that the

sources of following resets can be determined correctly .

6

EWDI

Enable Watchdog Timer Interrupt . If this bit is set to 1, an interrupt request can be generated when the

WDIF bit is set to 1 by any means . If this bit is cleared to 0, no interrupt occurs when WDIF is set to 1;

however, it does not stop the watchdog timer or prevent watchdog resets from occurring if EWT = 1 . If

EWT = 0 and EWDI = 0, the watchdog timer is stopped . If the watchdog timer is stopped (EWT = 0 and

EWDI = 0), setting the EWDI bit resets the watchdog interval and reset counter and enables the watchdog

timer . This bit is cleared to 0 by power-on reset and is unaffected by other forms of reset .

5:4

WD[1:0]

Watchdog Timer Interval Control Bits . These bits determine the watchdog timeout interval . The timeout

interval is set in terms of system clocks . Modifying the watchdog interval automatically resets the watch-

dog timer unless the 512 system clock reset counter is already in progress, in which case, changing the

WD[1:0] bits does not affect the watchdog timer or reset counter .

WD1

WD0

CLOCKSUNTILINTERRUPT

CLOCKSUNTILRESET

0

0

2

12

2

12

+ 512

0

1

2

15

2

15

+ 512

1

0

2

18

2

18

+ 512

1

1

2

21

2

21

+ 512

3

WDIF

Watchdog Interrupt Flag . This bit is set to 1 when the watchdog timer interval has elapsed or can be set to

1 by user software . When WDIF = 1, an interrupt request occurs if the watchdog interrupt has been enabled

(EWDI = 1) and not otherwise masked or prevented by an interrupt already in service (i .e ., IGE = 1, IMS = 1,

and INS = 0 must be true for the interrupt to occur) . This bit should be cleared by software before exiting the

interrupt service routine to avoid repeated interrupts . Furthermore, if the watchdog reset has been enabled

(EWT = 1), a reset is scheduled to occur 512 system clock cycles following setting of the WDIF bit .

2

WTRF

Watchdog Timer Reset Flag . This bit is set to 1 when the watchdog resets the processor . Software can

check this bit following a reset to determine if the watchdog was the source of the reset . Setting this bit

to 1 in software does not cause a watchdog reset . This bit is cleared by power-on reset only and is unaf-

fected by other forms of reset . It should also be cleared by software following any reset so that the source

of the next reset can be correctly determined by software . This bit is only set to 1 when a watchdog reset

actually occurs . If EWT is cleared to 0 when the watchdog timer elapses, this bit is not set .

1

EWT

Enable Watchdog Timer Reset . If this bit is set to 1 when the watchdog timer elapses, the watchdog resets

the MAX31782 512 system clock cycles later unless action is taken to disable the reset event . Clearing this

bit to 0 prevents a watchdog reset from occurring but does not stop the watchdog timer or prevent watch-

dog interrupts from occurring if EWDI = 1 . If EWT = 0 and EWDI = 0, the watchdog timer is stopped . If the

watchdog timer is stopped (EWT = 0 and EWDI = 0), setting the EWT bit resets the watchdog interval and

reset counter and enables the watchdog timer . This bit is cleared on power-on reset and is unaffected by

other forms of reset .

0

RWT

Reset Watchdog Timer . Setting this bit to 1 resets the watchdog timer count . If watchdog interrupt and/or

reset modes are enabled, the software must set this bit to 1 before the watchdog timer elapses to prevent

an interrupt or reset from occurring . This bit always returns 0 when read .