2 tap state control, 1 test-logic-reset, 2 run-test-idle – Maxim Integrated MAX31782 User Manual

Page 132: 3 ir-scan sequence, 16 .2 tap state control -4, 2tapstatecontrol, 1test-logic-reset, 2run-test-idle, 3ir-scansequence

MaximIntegrated 16-4

MAX31782 User’s Guide

Revision 0; 8/11

16.2TAPStateControl

The TAP provides an independent serial channel to communicate synchronously with the host system . The TAP state

control is achieved through host manipulation of the test mode select (TMS) and test clock (TCK) signals . The TMS

signal is sampled at the rising edge of TCK and decoded by the TAP controller to control movement between the TAP

states . The TDI input and TDO output are meaningful once the TAP is in a serial shift state (i .e ., Shift-IR or Shift-DR) .

16.2.1Test-Logic-Reset

On a power-on reset, the TAP controller is initialized to the Test-Logic-Reset state and the instruction register (IR[2:0])

is initialized to the Bypass instruction so that it does not affect normal system operation . No matter what the state of the

controller, it enters Test-Logic-Reset when TMS is held high for at least five rising edges of TCK . The controller remains

in the Test-Logic-Reset state if TMS remains high . An erroneous low signal on the TMS can cause the controller to move

into the Run-Test-Idle state, but no disturbance is caused to system operation if the TMS signal is returned and kept

at the intended logic-high for three rising edges of TCK, since this returns the controller to the Test-Logic-Reset state .

16.2.2Run-Test-Idle

As illustrated in

, the Run-Test-Idle state is simply an intermediate state for getting to one of the two state

sequences in which the controller performs meaningful operations:

• Controller state sequence (IR-Scan) or

• Data register state sequence (DR-Scan)

16.2.3IR-ScanSequence

The controller state sequence allows instructions (e .g ., Debug and System Programming) to be shifted into the instruc-

tion register starting from the Select-IR-Scan state . In the TAP, the instruction register is connected between the TDI

input and the TDO output . Inside the IR-Scan Sequence, the Capture-IR state loads a fixed binary pattern (001b) into the

3-bit shift register and the Shift-IR state causes shifting of TDI data into the shift register and serial output to TDO, least

significant bit first . Once the desired instruction is in the shift register, the instruction can be latched into the parallel

instruction register (IR[2:0]) on the falling edge of TCK in the Update-IR state . The contents of the 3-bit instruction shift

register and parallel instruction register (IR[2:0]) are summarized with respect to the TAP controller states in

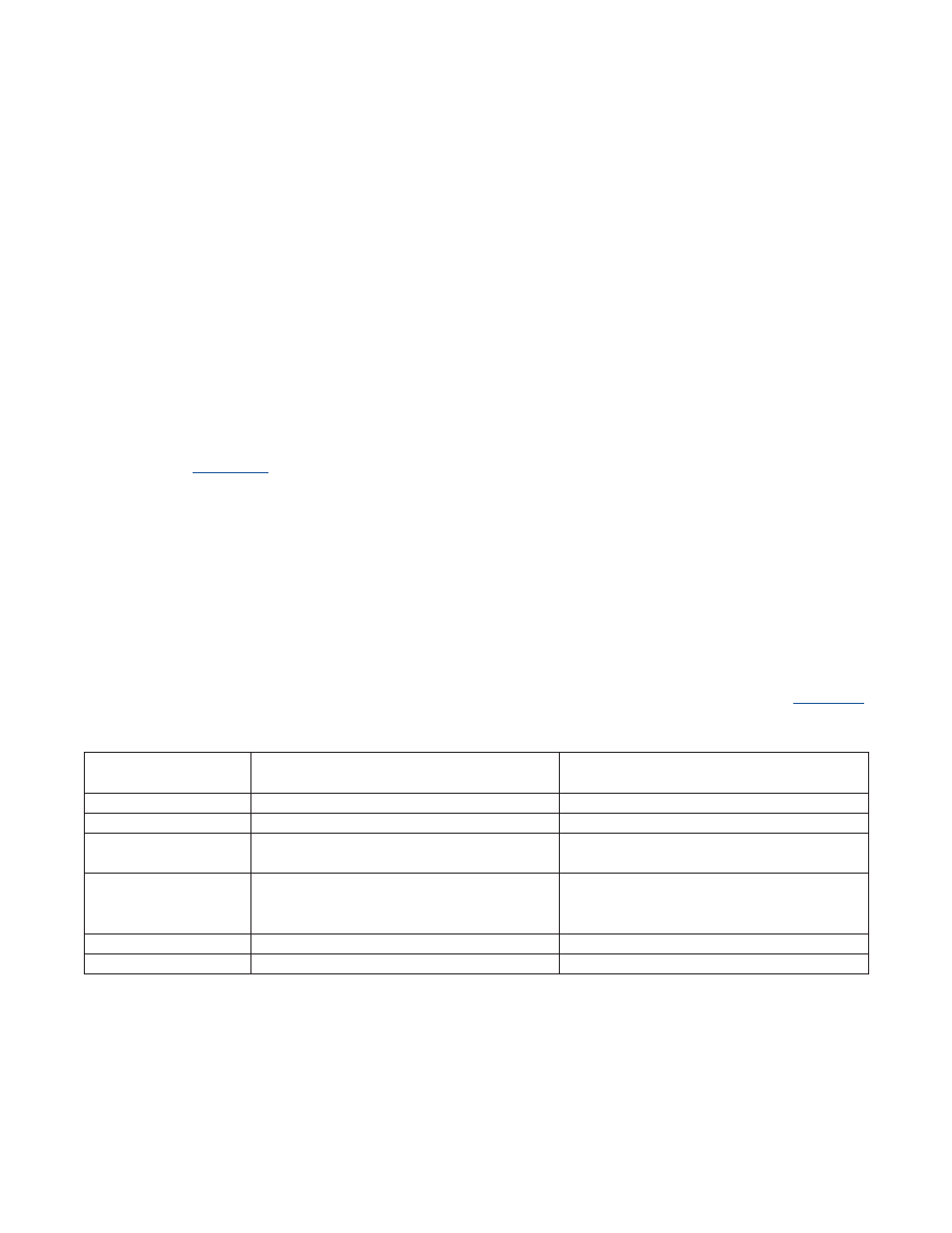

Table16-2.InstructionRegisterContentvs.TAPControllerState

TAPCONTROLLER

STATE

INSTRUCTIONSHIFTREGISTER

PARALLEL(3-BIT)

INSTRUCTIONREGISTER(IR[2:0])

Test-Logic-Reset

Undefined

Set to Bypass (011b) Instruction

Capture-IR

Load 001b at the rising edge of TCK

Retain last state

Shift-IR

Input data via TDI and Shift towards TDO at the ris-

ing edge of TCK

Retain last state

Exit1-IR

Exit2-IR

Pause-IR

Retain last state

Retain last state

Update-IR

Retain last state

Load from shift register at the falling edge of TCK

All other states

Undefined

Retain last state