Extended interrupt enable (eie), Movx extended address register (mxax), Xtended – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 82: Nterrupt, Nable, Eie), Movx e, Ddress, Egister, Mxax)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

82 of 158

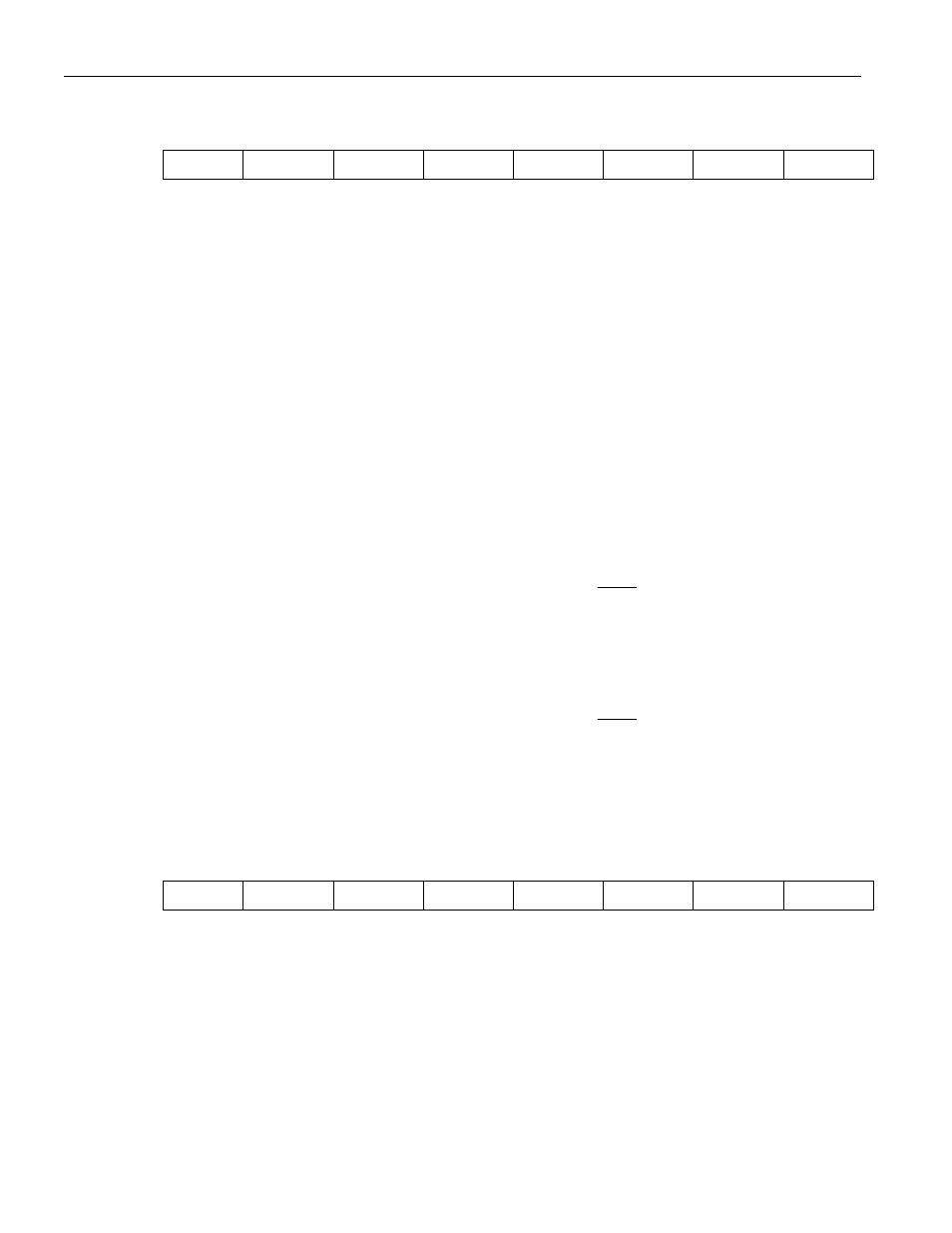

EXTENDED INTERRUPT ENABLE (EIE)

7 6 5 4 3 2 1 0

SFR

E8h

CANBIE

C0IE C1IE EWDI EX5 EX4 EX3 EX2

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

CANBIE

Bit 7

CAN 0/1 Activity Interrupt Priority. This bit enables/disables the CAN 0/1

Activity Interrupt

0 = Disable the CAN 0/1 Activity Interrupt.

1 = Enable the CAN 0/1 Activity Interrupt.

C0IE

Bit 6

CAN 0 Interrupt Enable. This bit enables/disables the CAN 0 Interrupt

0 = Disable the CAN 0 Interrupt.

1 = Enable the CAN 0 Interrupt.

C1IE

Bit 5

CAN 1 Interrupt Enable. This bit enables/disables the CAN 1 Interrupt

0 = Disable the CAN 1 Interrupt.

1 = Enable the CAN 1 Interrupt.

EWDI

Bit 4

Watchdog Interrupt Enable. This bit enables/disables the watchdog interrupt.

0 = Disable the watchdog interrupt.

1 = Enable interrupt requests generated by the watchdog timer.

EX5

Bit 3

External Interrupt 5 Enable. This bit enables/disables external interrupt 5.

0 = Disable external interrupt 5.

1 = Enable interrupt requests generated by the

5

INT pin.

EX4

Bit 2

External Interrupt 4 Enable. This bit enables/disables external interrupt 4.

0 = Disable external interrupt 4.

1 = Enable interrupt requests generated by the INT4 pin.

EX3

Bit 1

External Interrupt 3 Enable. This bit enables/disables external interrupt 3.

0 = Disable external interrupt 3.

1 = Enable interrupt requests generated by the

3

INT pin.

EX2

Bit 0

External Interrupt 2 Enable. This bit enables/disables external interrupt 2.

0 = Disable external interrupt 2.

1 = Enable interrupt requests generated by the INT2 pin.

MOVX EXTENDED ADDRESS REGISTER (MXAX)

7 6 5 4 3 2 1 0

SFR EAh

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

Bits 7-0

MOVX Extended Address Register. This register is concatenated with P2 and

R1 or R0 to form the 22-bit address when executing a MOVX @Ri, A or MOVX

A, @Ri instruction in either the 22-bit paged or 22-bit contiguous modes. The

DPTR related MOVX instructions do not utilize the P2 and MXAX register. Note

that the MXAX register is only used when the processor is operating in either the

paged or contiguous addressing modes.