Divide-by-13 option, Programmable clock output, Ivide – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 110: 13 o, Ption, Rogrammable, Lock, Utput

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

110 of 158

DIVIDE-BY-13 OPTION

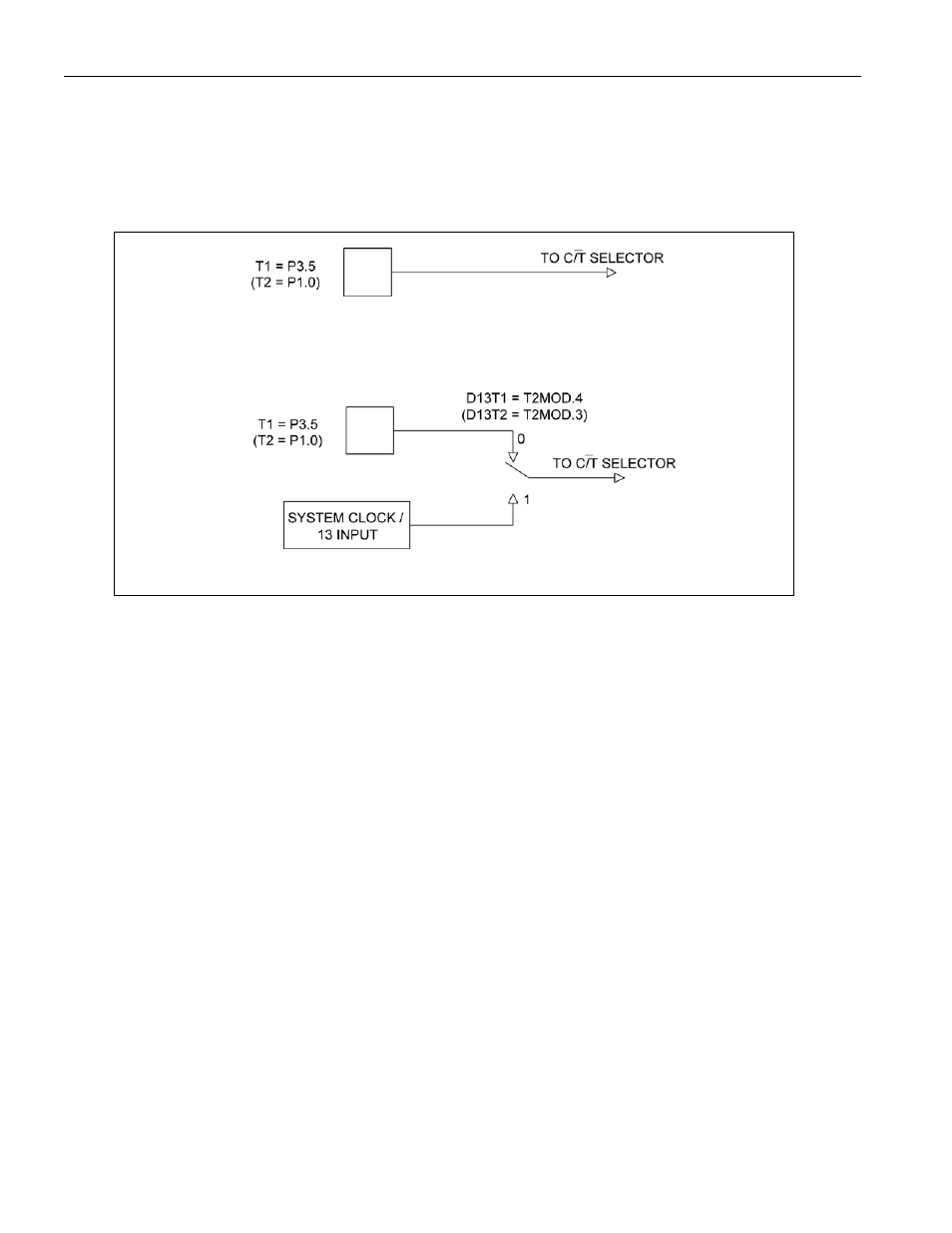

The other change to the timers associated with the DS80C390 is the inclusion of a divide-by-13 option for

Timer 1 and Timer 2. The option in independently enabled for each timer by setting the D13T1 (for timer

1) or D13T2 (for timer 2) bits. When enabled by setting the appropriate bits, the timer input from the T1

or T2 external pins will be replaced by a timebase that is OSC/13. The following figure illustrates the

operation of these bits.

The setting of the divide-by-13 bits will affect all operations of timer 1 and all operations of timer except

baud rate generator mode. The baud rate generator mode of Timer 2 will not be affected by any setting of

the D13T2 bit.

The divide-by-13 settings of Timer 1 and Timer 2 allow the microprocessor to simultaneously generate

standard serial baud rates and standard CAN baud rates within generally acceptable error tolerances. In an

original divide-by-12 timer an 11.0592MHz crystal frequency (or multiple thereof) was usually needed to

generate standard serial baud rates. The divide-by-13 setting offers the additional option of selecting the

microprocessor clock frequency by 12/13. Thus, using a 12MHz crystal and the divide-by-13 setting, the

effective baud rate becomes (12/13) x 12 = 11.0769MHz. This differs from the ideal baud rate frequency

by only 0.16%, an insignificant difference, but allows the use of a crystal frequency that is acceptable for

serial port and CAN operation. Using this feature, standard serial rates of up to 38.4k baud are available

with a 16MHz crystal. A 24MHz crystal allows serial rates up to 115.2k baud.

PROGRAMMABLE CLOCK OUTPUT

When enabled, the DS80C390 can output a 50% duty cycle square wave on external pin P3.5. This signal

is free-running, and not synchronized to the external clock source. To enable this feature, three conditions

must be met:

1. Select the output frequency of system clock divided by 2, 4, 6, or 8 by the Clock Output Divide Select

bits (COR.2-1).

2. The External Clock Output Enable bit, CLKOE, must be set (COR.0). Steps 1 and 2 can be combined

and must use the Timed Access procedure.

3. The P3.5 latch bit (P3.5) must be set.

As shown in the High-Speed Microcontroller User’s Guide.

As implemented in DS80C390 with the divide-by-13 option.