Can 1 t, Ransmit, Essage – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 72: Cknowledgement, Egister, 0 (c1tma0)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

72 of 158

WTRF

Bit 2

Watchdog Timer Reset Flag. When set, this bit indicates that a watchdog timer

reset has occurred. It is typically interrogated to determine if a reset was caused

by watchdog timer reset. It is cleared by a power- on reset, but otherwise must be

cleared by software before the next reset of any kind or software may erroneously

determine that a watchdog timer reset has occurred. Setting this bit in software

will not generate a watchdog timer reset. If the EWT bit is cleared, the watchdog

timer will have no effect on this bit.

EWT

Bit 1

Enable Watchdog Timer Reset. This bit enables/disables the ability of the

watchdog timer to reset the device. This bit has no effect on the ability of the

watchdog timer to generate a watchdog interrupt. The time-out period of the

watchdog timer is controlled by the Watchdog Timer Mode Select bits

(CKCON.7-6). Clearing this bit will disable the ability of the watchdog timer to

generate a reset, but have no affect on the timer itself, or its ability to generate a

watchdog timer interrupt. This bit can only be modified using a Timed Access

Procedure. This bit is unaffected by all other resets.

0 = A timeout of the watchdog timer will not cause the device to reset.

1 = A timeout of the watchdog timer will cause the device to reset.

RWT

Bit 0

Reset Watchdog Timer. Setting this bit will reset the watchdog timer count.

This bit must be set using a Timed Access procedure before the watchdog timer

expires, or a watchdog timer reset and/or interrupt will be generated if enabled.

The time-out period is defined by the Watchdog Timer Mode Select bits

(CKCON.7-6). This bit will always be 0 when read.

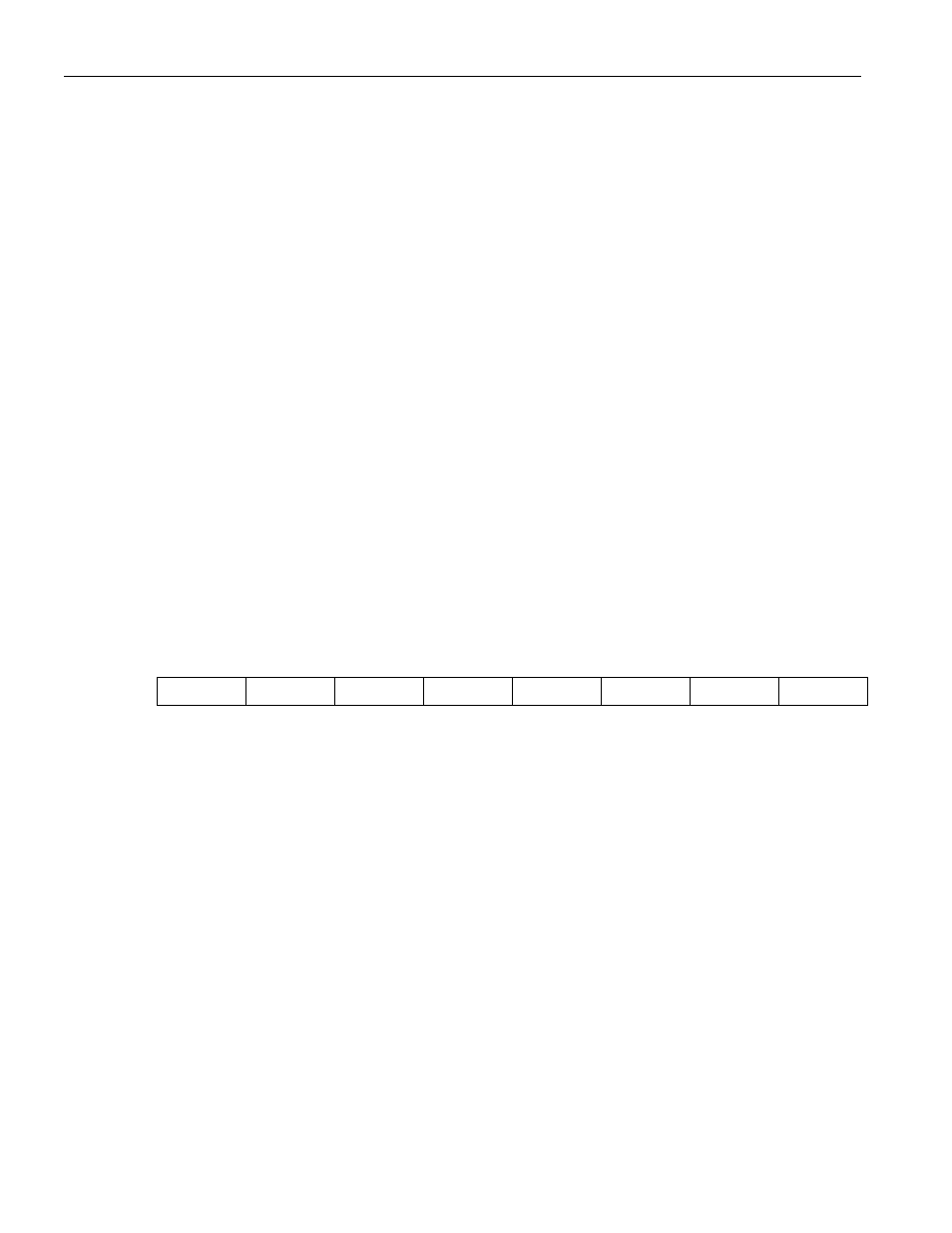

CAN 1 TRANSMIT MESSAGE ACKNOWLEDGEMENT REGISTER 0 (C1TMA0)

7 6 5 4 3 2 1 0

SFR DEh

—

— — — — — — —

R-0 R-0 R-0 R-0 R-0 R-0 R-0 R-0

R = Unrestricted Read, -n= Value after Reset

CAN 1 Transmit Message Acknowledgement Register 0. This register

indicates which of CAN 1 message centers 1-8 have successfully transmitted

a message since the last read of this register. A logic one in a location

indicates a message has been transmitted from that message center. This

register is automatically cleared to 00h when read. This register should

always be read in conjunction with the C1TMA1 register to ascertain the

status of all message centers.

C1TMA0.7

Bit 7

Message Center 8, Message Transmitted

C1TMA0.6

Bit 6

Message Center 7, Message Transmitted

C1TMA0.5

Bit 5

Message Center 6, Message Transmitted

C1TMA0.4

Bit 4

Message Center 5, Message Transmitted