Timer 2 msb (th2), Clock output register (cor), Imer – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 64: 2 msb (th2), Lock, Utput, Egister, Cor)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

64 of 158

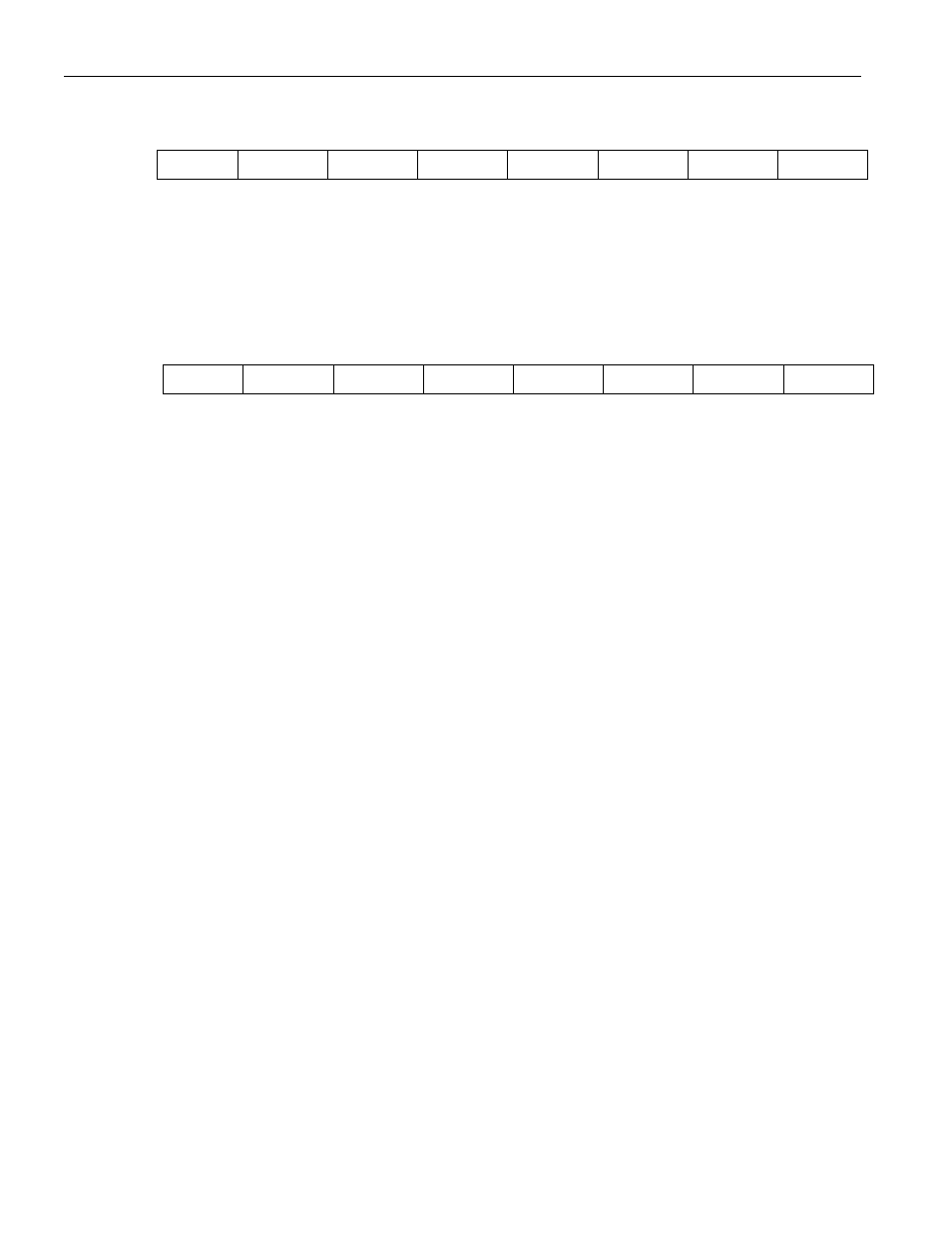

TIMER 2 MSB (TH2)

7 6 5 4 3 2 1 0

SFR CDh

TH2.7

TH2.6

TH2.5

TH2.4 TH2.3 TH2.2 TH2.1 TH2.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R = Unrestricted Read, W = Unrestricted Write, -n = Value after Reset

TL2.7-0

Bits 7-0

Timer 2 MSB. This register contains the least significant byte of Timer 2.

CLOCK OUTPUT REGISTER (COR)

7 6 5 4 3 2 1 0

SFR CEh IRDACK C1BPR7 C1BPR6 C0BPR7 C0BPR6 COD1 COD0 CLKOE

RT-0 RT-0 RT-0 RT-0 RT-0 RT-0 RT-0 RT-0

R = Unrestricted Read, T = Timed Access Write Only, -n = Value after Reset

IRDACK

Bit 7

IRDA Clock Output Enable. This bit determines which clock signal will be

asserted on port pin P3.5 when the CLKOE bit is set. Please consult the

description of the CLKOE bit for more information.

0 = The port pin P3.5 will output a signal determined by the Clock Output Divide

Bits (COR.1 and COR.2).

1 = The port pin P3.5 will output a signal that is 16 times the programmed baud

rate associated with Serial Port 0.

C1BPR7, C1BPR6

Bit 6-5

CAN 1 Baud Rate Prescaler Bits. These bits establish bits 7 and 6 of the eight-

bit CAN 1 Baud Rate Prescaler. These bits can not be modified while the SWINT

bit in the CAN1 Control Register is cleared to 0. The remaining six bits are

located in the CAN 1 Bus Timing Register Zero (C1BT0) located in the CAN

MOVX memory.

C0BPR7, C0BPR6

Bit 4-3

CAN 0 Baud Rate Prescaler Bits. These bits establish bits 7 and 6 of the eight-

bit CAN 0 Baud Rate Prescaler. These bits can not be modified while the SWINT

bit in the CAN 0 Control Register is cleared to 0. The remaining six bits are

located in the CAN 0 Bus Timing Register Zero (C0BT0) located in the CAN

MOVX memory.

COD1, COD0

Bit 2-1

Clock Output Divide Select bits. These bits select the frequency of signal

asserted on port pin P3.5 when CLKOE=1 and IRDACK=0. Please consult the

description of the CLKOE bit for more information.

COD1

COD0

P3.5 Output Frequency

0

0

System clock divided by 2

0

1

System clock divided by 4

1

0

System clock divided by 6

1

1

System clock divided by 8