Can 0 message center 1 control register (c0m1c), Can 0 m, Essage – Maxim Integrated High-Speed Microcontroller Users Guide: DS80C390 Supplement User Manual

Page 46: Enter, Ontrol, Egister, C0m1c)

High-Speed Microcontroller User’s Guide: DS80C390 Supplement

46 of 158

CAN 0 MESSAGE CENTER 1 CONTROL REGISTER (C0M1C)

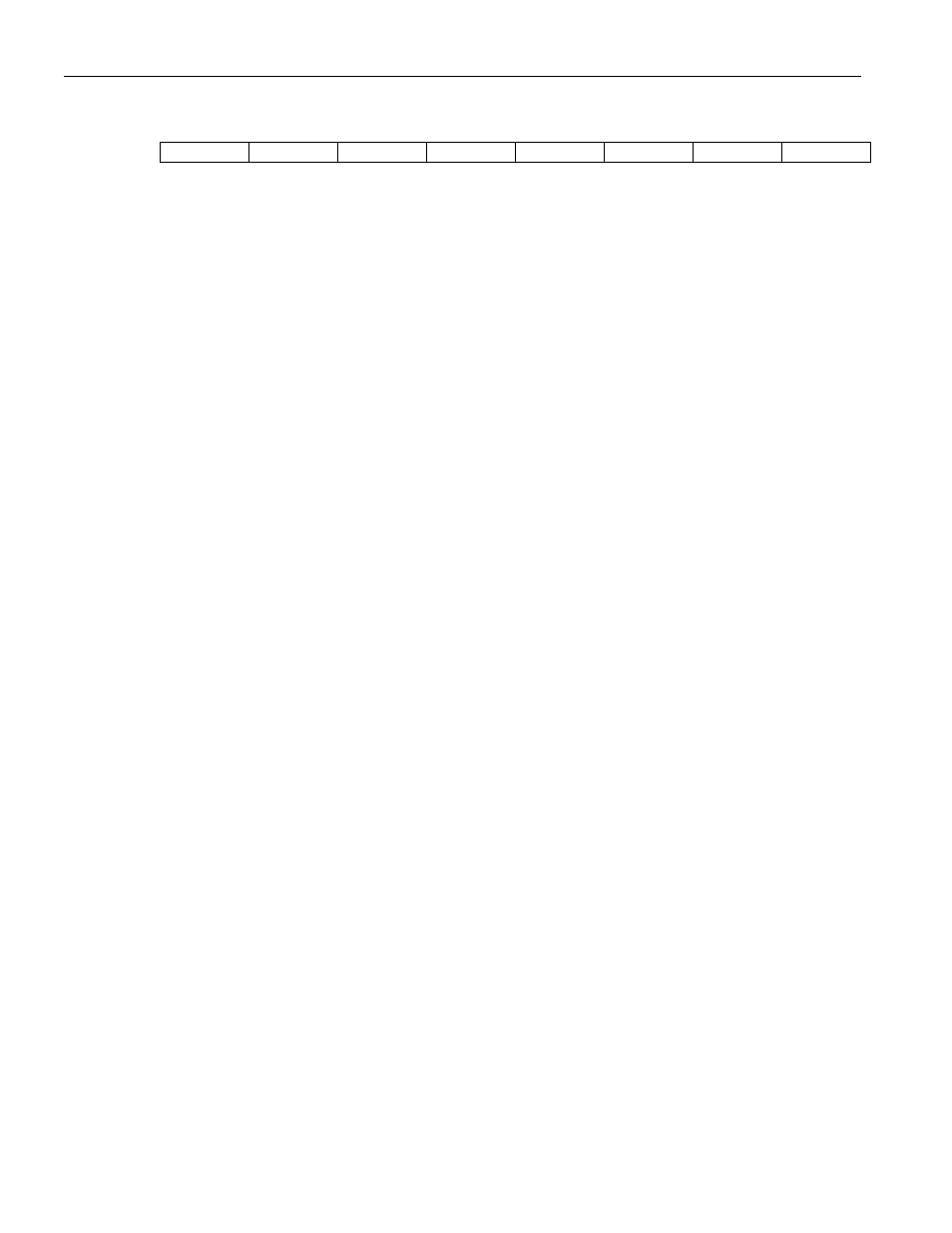

7 6 5 4 3 2 1 0

SFR ABh

MSRDY

ETI

ERI

INTRQ

EXTRQ

MTRQ

ROW/TIH

DTUP

RW-0 RW-0 RW-0 RW-0 RC-0 R*-0 R*-0 R*-0

R = Unrestricted Read, C = Clear Only, * = See description below, -n = Value after Reset

MSRDY

Bit 7

CAN 0 Message Center 1 Ready. This bit is used by the Microcontroller to

prevent the CAN module from accessing message center 1 while the

microcontroller is updating message attributes. These include as identifiers

(arbitration registers 0-3), data byte registers 0-7, data byte count (DTBYC3-

DTBYC0), direction control (T/R), the extended or standard mode bit

(EX/ST), and the mask enables (MEME and MDME) associated with this

message center. When this bit is 0, the CAN 0 processor will ignore this

message center for transmit, receive, or remote frame request operations.

MSRDY is cleared following a microcontroller hardware reset or a reset

generated by the CRST bit in the CAN 0 Control Register, and must also

remain in a cleared mode until all the CAN 0 initialization has been

completed. Individual message MSRDY controls can be changed after

initialization to reconfigure specific messages, without interrupting the

communication of other messages on the CAN 0 Bus.

ETI

Bit 6

CAN 0 Message Center 1 Enable Transmit Interrupt. Setting ETI to a 1 will

enable a successful CAN 0 transmission in message center 1 to set the INTRQ bit

for this message center, which in turn issues an interrupt to the microcontroller.

When ETI is cleared to 0 a successful transmission will not set INTRQ bit and

will not generate an interrupt. Note that the ETI bit located in Message Center 15

is ignored by the CAN module, since the message center 15 is a receive only

message center.

ERI

Bit 5

CAN 0 Message Center 1 Enable Receive Interrupt. Setting ERI to a 1

will enable a successful CAN 0 reception and storage in message center 1 to

set the INTRQ bit for this message center which in turn will issue an interrupt

to the microcontroller. When ERI is cleared to 0 a successful reception will

not set the INTRQ bit and as such will not generate an interrupt.

INTRQ

Bit 4

CAN 0 Message Center 1 Interrupt Request. This bit serves as a CAN

interrupt flag, indicating the successful transmission or reception of a

message in this message center. INTRQ is automatically set when ERI=1 and

message center 1 successfully receives and stores a message. The INTRQ bit

is also set to a 1 when ETI is set and the CAN 1 logic completes a successful

transmission. The INTRQ interrupt request must be also enabled by the EA

global mask in the IE SFR register if the interrupt is to be acknowledged by

the microcontroller interrupt logic. This flag must be cleared by software.

EXTRQ

Bit 3

CAN 0 Message Center 1 External Transmit Request. When EXTRQ is

cleared to a 0, there are no pending requests by external CAN nodes for this

message. When EXTRQ is set to a 1, a request has been made for this

message by an external CAN node, but the CAN 0 controller has not yet

completed the service request. Following the completion of a requested